VII LCD CONTROLLER BLOCK: LCD CONTROLLER

S1C33L03 FUNCTION PART EPSON B-VII-2-7

A-1

B-VII

LCDC

Clock

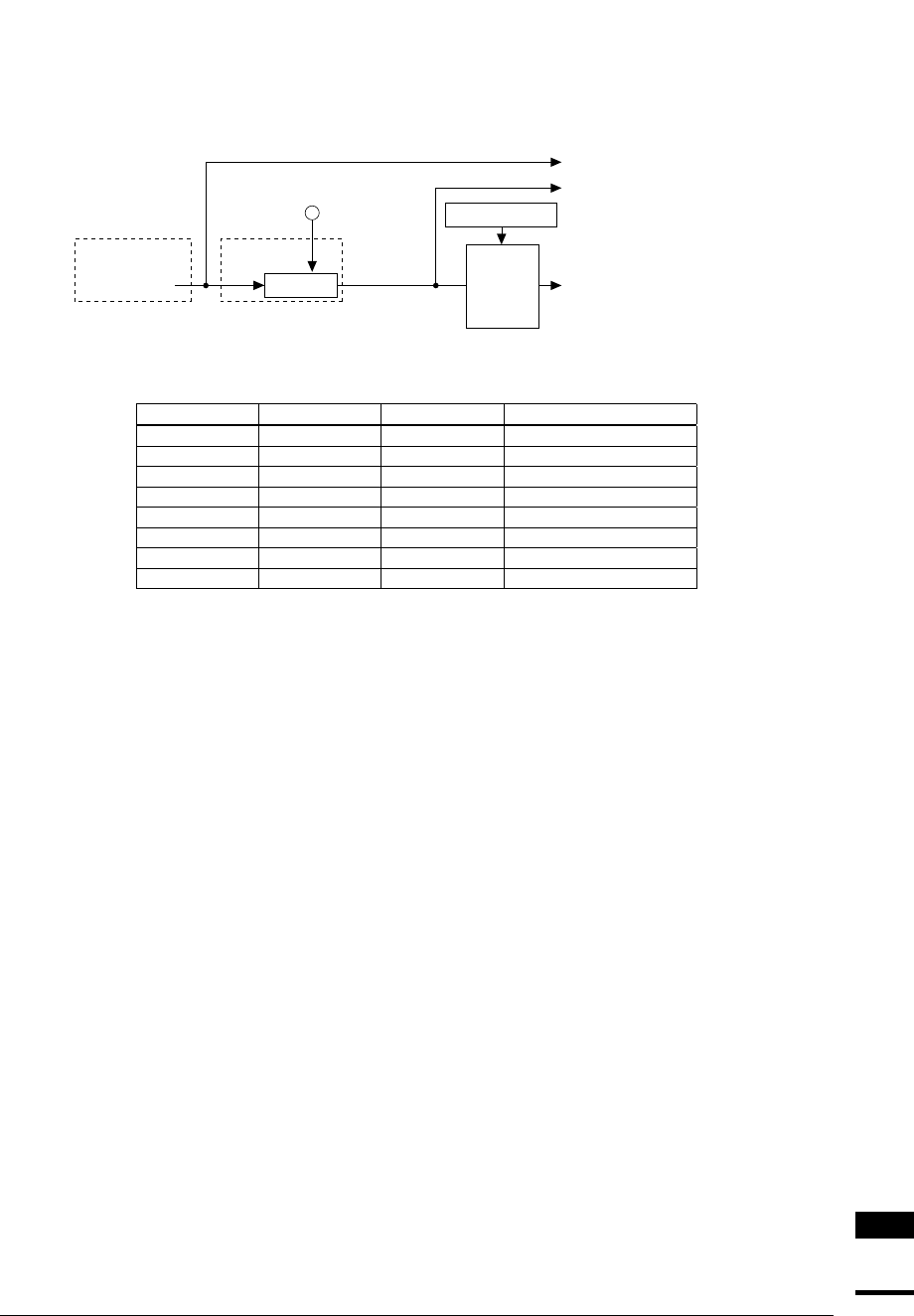

The LCD controller uses the BCU clock as the source clock for its pixel clock PCLK and display memory clock

MCLK. The maximum clock frequency that can be supplied to the LCD controller is 25 MHz. The BCU clock

divide ratios can be set using the LCLKSEL[2:0] (D[2:0])/FIFO control register (0x39FFF4), as shown in Table

2.3 below.

LCLKSEL[2:0]

#X2SPD pin

To CPU

CPU_CLK

BCU_CLK

Bus clock

LCDC clock (PCLK, MCLK)

BCUCLG

1/1 or 1/2

1/1

1/2

1/3

1/4

Figure 2.3 LCDC Clocks

Table 2.3 Selection of LCDC Clocks

LCLKSEL2 LCLKSEL1 LCLKSEL0 LCDC clock

000Turned off

001Turned off

010Turned off

011Reserved (not allowed)

100BCU_CLK

101BCU_CLK/2

110BCU_CLK/3

111BCU_CLK/4