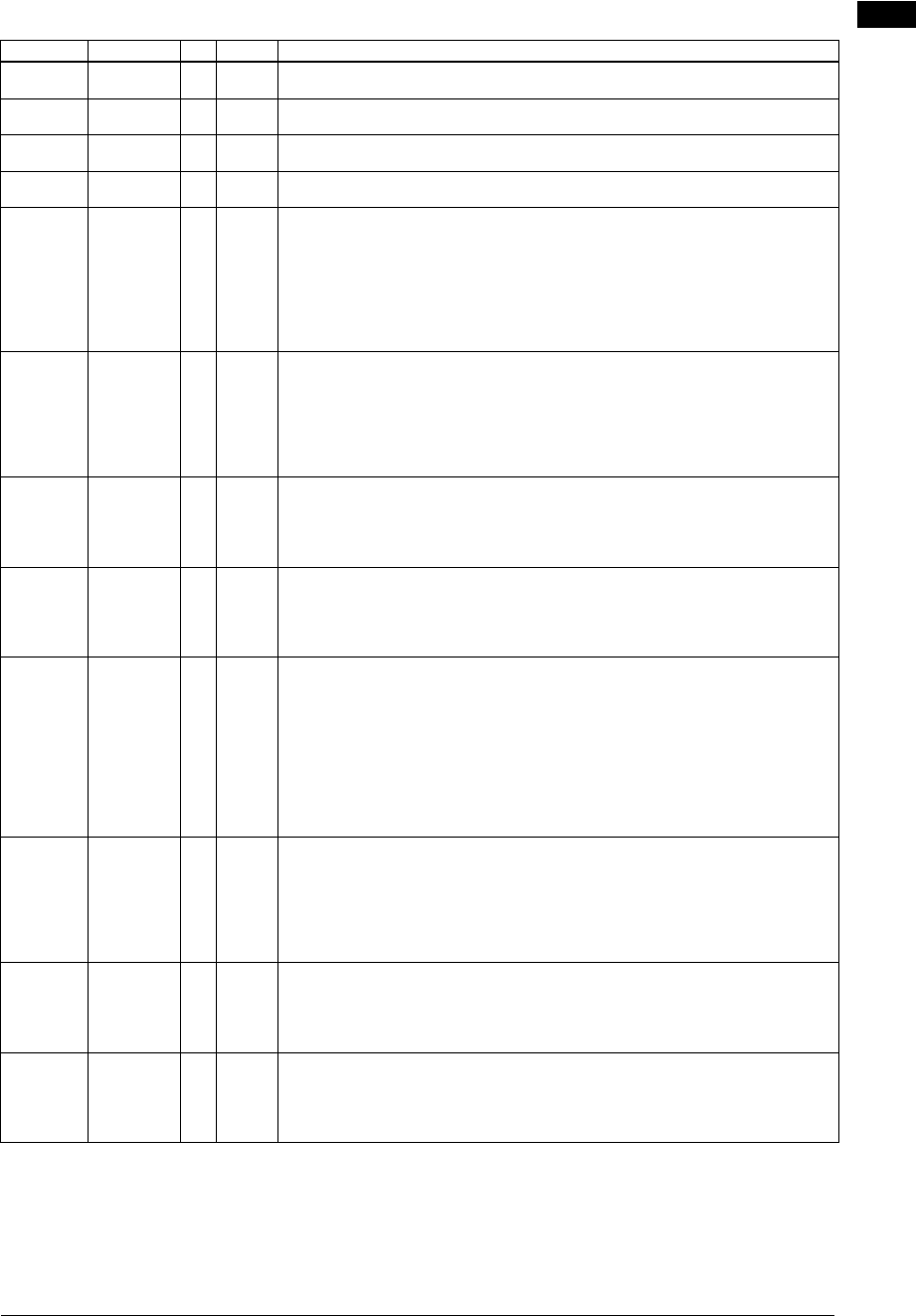

1 OUTLINE

S1C33L03 PRODUCT PART EPSON A-7

A-1

Table 1.3.3 List of Pins for HSDMA Control Signals

Pin name Pin No. I/O Pull-up Function

K50

#DMAREQ0

41 I Pull-up K50: Input port when CFK50(D0/0x402C0) = "0" (default)

#DMAREQ0: HSDMA Ch. 0 request input when CFK50(D0/0x402C0) = "1"

K51

#DMAREQ1

40 I Pull-up K51: Input port when CFK51(D1/0x402C0) = "0" (default)

#DMAREQ1: HSDMA Ch. 1 request input when CFK51(D1/0x402C0) = "1"

K53

#DMAREQ2

38 I Pull-up K53: Input port when CFK53(D3/0x402C0) = "0" (default)

#DMAREQ2: HSDMA Ch. 2 request input when CFK53(D3/0x402C0) = "1"

K54

#DMAREQ3

37 I Pull-up K54: Input port when CFK54(D4/0x402C0) = "0" (default)

#DMAREQ3: HSDMA Ch. 3 request input when CFK54(D4/0x402C0) = "1"

P32

#DMAACK0

#SRDY3

HDQM

73 I/O – P32: I/O port when CFP32(D2/0x402DC) = "0" and SDRENA(D7/0x39FFC1) = "0"

(default)

#DMAACK0: HSDMA Ch. 0 acknowledge output when CFP32(D2/0x402DC) = "1" and

SDRENA(D7/0x39FFC1) = "0"

#SRDY3: Serial I/F Ch. 3 ready signal input/output when SSRDY3(D3/0x402D7) =

"1", CFP32(D2/0x402DC) = "0" and SDRENA(D7/0x39FFC1) = "0"

HDQM: SDRAM data (high byte) input/output mask signal when

SDRENA(D7/0x39FFC1) = "1"

P33

#DMAACK1

SIN3

SDA10

72 I/O – P33: I/O port when CFP33(D3/0x402DC) = "0" and SDRENA(D7/0x39FFC1) = "0"

(default)

#DMAACK1: HSDMA Ch. 1 acknowledge output when CFP33(D3/0x402DC) = "1" and

SDRENA(D7/0x39FFC1) = "0"

SIN3:Serial I/F Ch. 3 data input when SSIN3(D0/0x402D7) = "1",

CFP33(D3/0x402DC) = "0" and SDRENA(D7/0x39FFC1) = "0"

SDA10: SDRAM address bus bit 10 when SDRENA(D7/0x39FFC1) = "1"

P04

SIN1

#DMAACK2

12 I/O – P04: I/O port when CFP04(D4/0x402D0) = "0" and CFEX4(D4/0x402DF) = "0"

(default)

SIN1:Serial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and

CFEX4(D4/0x402DF) = "0"

#DMAACK2: HSDMA Ch. 2 acknowledge output when CFEX4(D4/0x402DF) = "1"

P06

#SCLK1

#DMAACK3

10 I/O – P06: I/O port when CFP06(D6/0x402D0) = "0" and CFEX6(D6/0x402DF) = "0"

(default)

#SCLK1: Serial I/F Ch. 1 clock input/output when CFP06(D6/0x402D0) = "1" and

CFEX6(D6/0x402DF) = "0"

#DMAACK3: HSDMA Ch. 3 acknowledge output when CFEX6(D6/0x402DF) = "1"

P15

EXCL4

#DMAEND0

#SCLK3

LDQM

84 I/O – P15: I/O port when CFP15(D5/0x402D4) = "0" and SDRENA(D7/0x39FFC1) = "0"

(default)

EXCL4: 16-bit timer 4 event counter input when CFP15(D5/0x402D4) = "1",

IOC15(D5/0x402D6) = "0" and SDRENA(D7/0x39FFC1) = "0"

#DMAEND0: HSDMA Ch. 0 end-of-transfer signal output when CFP15(D5/0x402D4) =

"1", IOC15(D5/0x402D6) = "1" and SDRENA(D7/0x39FFC1) = "0"

#SCLK3: Serial I/F Ch. 3 clock input/output when SSCLK3(D2/0x402D7) = "1",

CFP15(D5/0x402D4) = "0" and SDRENA(D7/0x39FFC1) = "0"

LDQM: SDRAM data (low byte) input/output mask signal when

SDRENA(D7/0x39FFC1) = "1"

P16

EXCL5

#DMAEND1

SOUT3

83 I/O – P16: I/O port when CFP16(D6/0x402D4) = "0" (default)

EXCL5: 16-bit timer 5 event counter input when CFP16(D6/0x402D4) = "1" and

IOC16(D6/0x402D6) = "0"

#DMAEND1: HSDMA Ch. 1 end-of-transfer signal output when CFP16(D6/0x402D4) = "1"

and IOC16(D6/0x402D6) = "1"

SOUT3: Serial I/F Ch. 3 data output when SSOUT3(D1/0x402D7) = "1" and

CFP16(D6/0x402D4) = "0"

P05

SOUT1

#DMAEND2

11 I/O – P05: I/O port when CFP05(D5/0x402D0) = "0" and CFEX5(D5/0x402DF) = "0"

(default)

SOUT1: Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and

CFEX5(D5/0x402DF) = "0"

#DMAEND2: HSDMA Ch. 2 end-of-transfer signal output when CFEX5(D5/0x402DF) = "1"

P07

#SRDY1

#DMAEND3

9 I/O – P07: I/O port when CFP07(D7/0x402D0) = "0" and CFEX7(D7/0x402DF) = "0"

(default)

#SRDY1: Serial I/F Ch. 1 ready signal output when CFP07(D7/0x402D0) = "1" and

CFEX5(D5/0x402DF) = "0"

#DMAEND3: HSDMA Ch. 3 end-of-transfer signal output when CFEX7(D7/0x402DF) = "1"