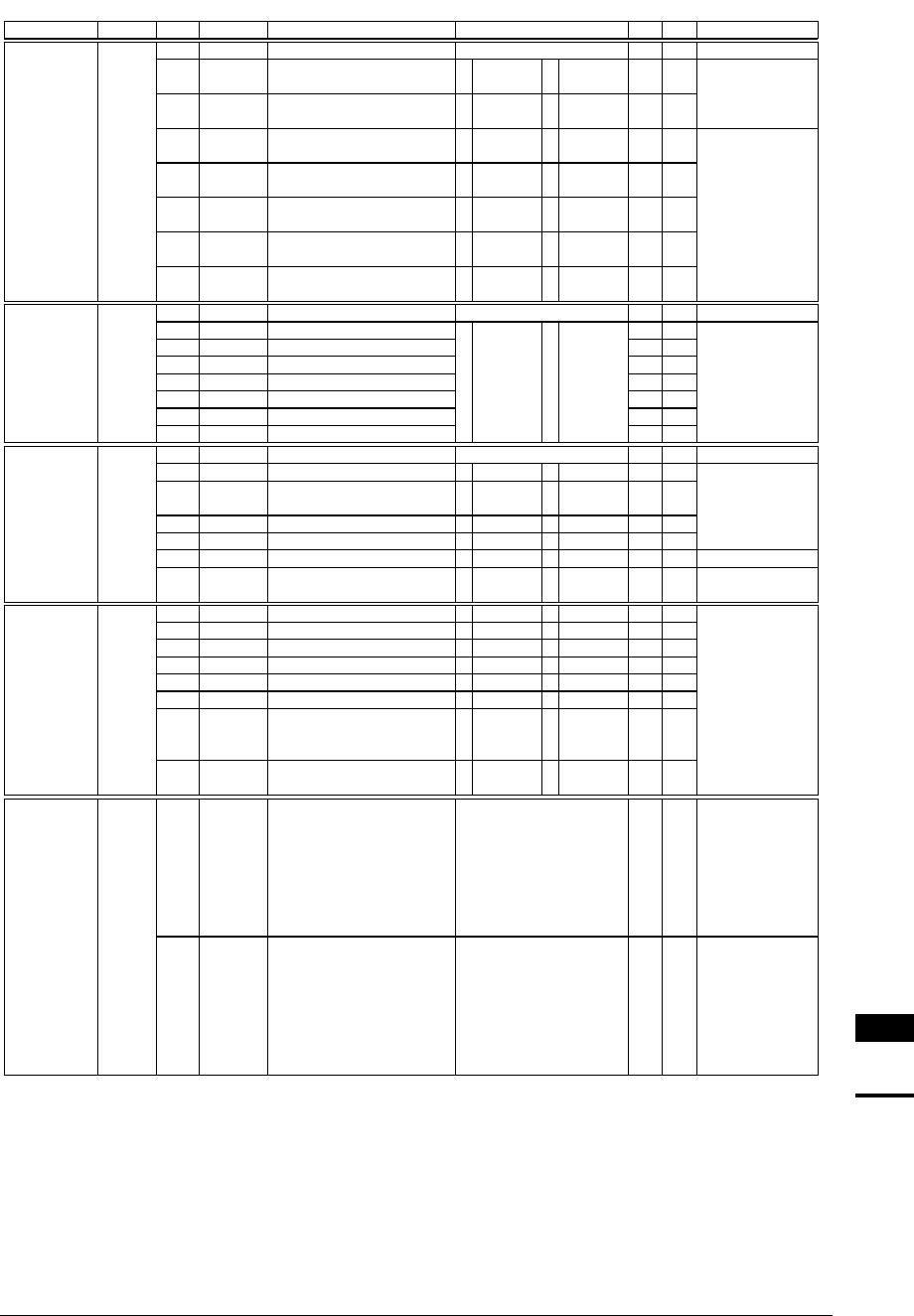

V DMA BLOCK: HSDMA (High-Speed DMA)

S1C33L03 FUNCTION PART EPSON B-V-2-19

A-1

B-V

HSDMA

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

CFP16

CFP15

CFP14

CFP13

CFP12

CFP11

CFP10

D7

D6

D5

D4

D3

D2

D1

D0

reserved

P16 function selection

P15 function selection

P14 function selection

P13 function selection

P12 function selection

P11 function selection

P10 function selection

–

0

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.

Extended functions

(0x402DF)

00402D4

(B)

1 EXCL5

#DMAEND1

0 P16

1 EXCL4

#DMAEND0

0 P15

1 EXCL3

T8UF3

0 P13

1 EXCL2

T8UF2

0 P12

1 EXCL1

T8UF1

0 P11

1 EXCL0

T8UF0

0 P10

–P1 function

select register

1 FOSC1 0 P14

–

IOC16

IOC15

IOC14

IOC13

IOC12

IOC11

IOC10

D7

D6

D5

D4

D3

D2

D1

D0

reserved

P16 I/O control

P15 I/O control

P14 I/O control

P13 I/O control

P12 I/O control

P11 I/O control

P10 I/O control

–

0

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.

This register

indicates the values

of the I/O control

signals of the ports

when it is read. (See

detailed explanation.)

00402D6

(B)

1 Output 0 Input

–P1 I/O control

register

–

CFP35

CFP34

CFP33

CFP32

CFP31

CFP30

D7–6

D5

D4

D3

D2

D1

D0

reserved

P35 function selection

P34 function selection

P33 function selection

P32 function selection

P31 function selection

P30 function selection

–

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.

Ext. func.(0x402DF)

00402DC

(B)

–P3 function

select register

1 #BUSACK 0 P35

1 #BUSREQ

#CE6

0 P34

1

#DMAACK0

0 P32

1 #BUSGET 0 P31

1 #WAIT

#CE4/#CE5

0 P30

1

#DMAACK1

0 P33

CFEX7

CFEX6

CFEX5

CFEX4

CFEX3

CFEX2

CFEX1

CFEX0

D7

D6

D5

D4

D3

D2

D1

D0

P07 port extended function

P06 port extended function

P05 port extended function

P04 port extended function

P31 port extended function

P21 port extended function

P10, P11, P13 port extended

function

P12, P14 port extended function

0

0

0

0

0

0

1

1

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

00402DF

(B)

Port function

extension

register

1

#DMAEND3

0 P07, etc.

1

#DMAACK3

0 P06, etc.

1

#DMAEND2

0 P05, etc.

1

#DMAACK2

0 P04, etc.

1 #GARD 0 P31, etc.

1 #GAAS 0 P21, etc.

1 DST0

DST1

DPC0

0 P10, etc.

P11, etc.

P13, etc.

1 DST2

DCLK

0 P12, etc.

P14, etc.

TC0_L7

TC0_L6

TC0_L5

TC0_L4

TC0_L3

TC0_L2

TC0_L1

TC0_L0

BLKLEN07

BLKLEN06

BLKLEN05

BLKLEN04

BLKLEN03

BLKLEN02

BLKLEN01

BLKLEN00

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Ch.0 transfer c

ounter[7:0]

(block transfer mode)

Ch.0 transfer counter[15:8]

(single/successive transfer mode)

Ch.0 block length

(block transfer mode)

Ch.0 transfer counter[7:0]

(single/successive transfer mode)

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

R/W

R/W

0048220

(HW)

High-speed

DMA Ch.0

transfer

counter

register