II CORE BLOCK: BCU (Bus Control Unit)

S1C33L03 FUNCTION PART EPSON B-II-4-41

A-1

B-II

BCU

RCA1–RCA0: Column address size selection (D[B:A]) / Bus control register (0x4812E)

Select the column address size of DRAM.

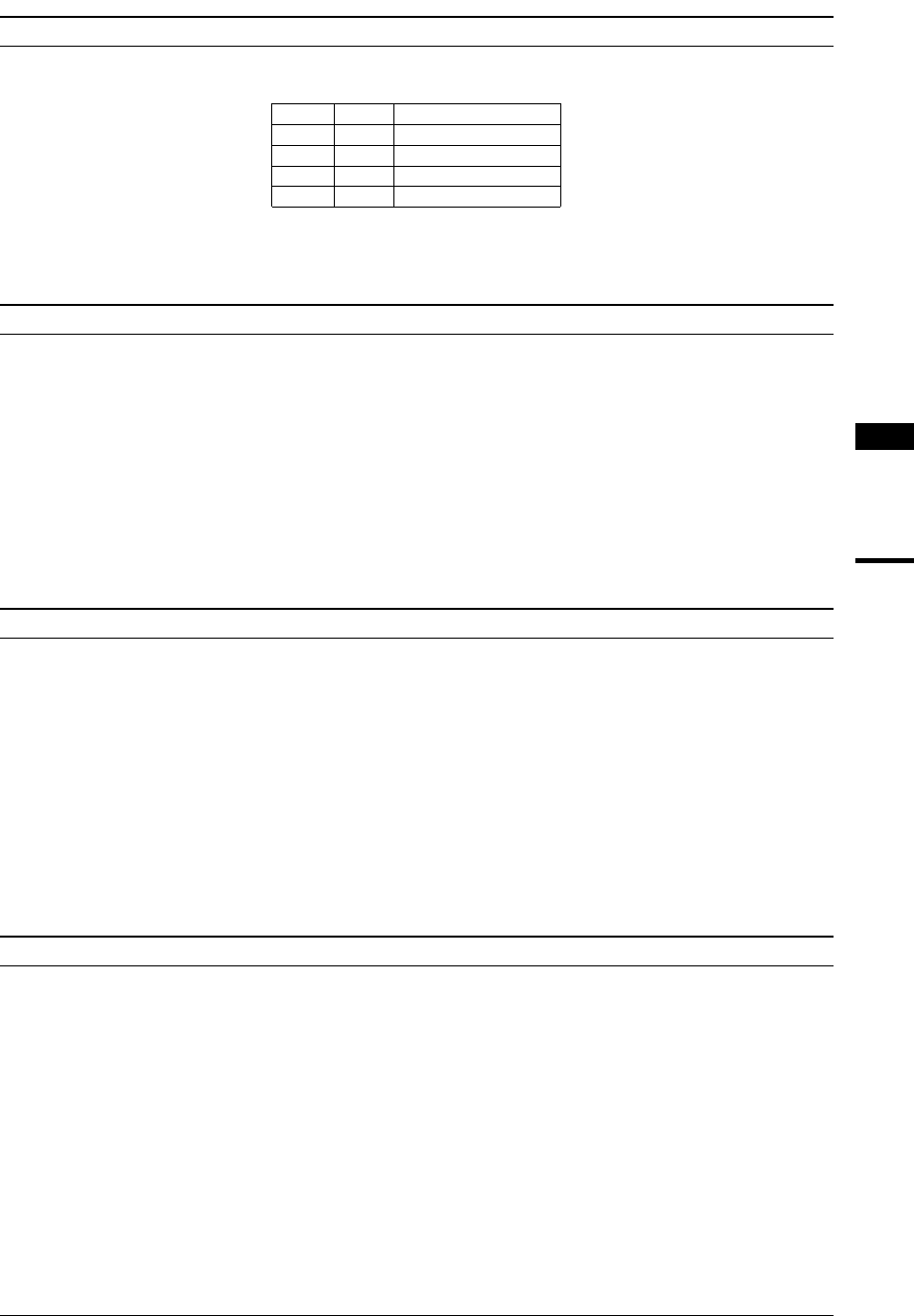

Table 4.26 Column Address Size

RCA1 RCA0 Column address size

11 11

10 10

01 9

00 8

The contents set here are applied to all of areas 14, 13, 8, and 7 that are set for DRAM.

RCA can be read to obtain its set value.

At cold start, RCA is set to "0" (8 bits). At hot start, RCA retain its status before being initialized.

RPC2: Refresh enable (D9) / Bus control register (0x4812E)

Control the DRAM refresh function.

Write "1": Enabled

Write "0": Disabled

Read: Valid

When DRAM is connected directly, a refresh cycle is generated by writing "1" to RPC2. The internal refresh

function is disabled by writing "0" to RPC2.

Since the BCU stops operating in the HALT2 and the SLEEP modes, no refresh cycle is generated regardless of

how this bit is set.

The contents set here are applied to all of areas 14, 13, 8, and 7 that are set for DRAM.

At cold start, RPC2 is set to "0" (disabled). At hot start, RPC2 retains its status before being initialized.

RPC1: Refresh method selection (D8) / Bus control register (0x4812E)

Select the DRAM refresh method.

Write "1": Self-refresh

Write "0": CAS-before-RAS refresh

Read: Valid

To perform a CAS-before-RAS refresh, set RPC1 to "0" and then RPC2 to "1". This causes the underflow output

signal of the 8-bit programmable timer 0 is fed to the DRAM interface, at which timing a refresh cycle is

generated.

To start a self-refresh, set RPC1 to "1" and then RPC2 to "1". The self-refresh is disabled by writing "0" to RPC2.

The contents set here are applied to all of areas 14, 13, 8, and 7 that are set for DRAM.

At cold start, RPC1 is set to "0" (CAS-before-RAS refresh). At hot start, RPC1 retains its status before being

initialized.

RPC0: Refresh RPC delay (D7) / Bus control register (0x4812E)

Set a RPC delay when at start of refresh.

Write "1": 2 cycles

Write "0": 1 cycle

Read: Valid

Set a time from the immediately preceding precharge to the falling transition of #HCAS/#LCAS necessary in order

to perform a refresh. This time is 2 cycles when RPC0 = "1" or 1 cycle when RPC0 = "0".

The contents set here are applied to all of areas 14, 13, 8, and 7 that are set for DRAM.

At cold start, RPC0 is set to "0" (1 cycle). At hot start, RPC0 retains its status before being initialized.