5 POWER-DOWN CONTROL

S1C33L03 PRODUCT PART EPSON A-65

A-1

A-5

5 Power-Down Control

This chapter describes the controls used to reduce power consumption of the device.

Points on power saving

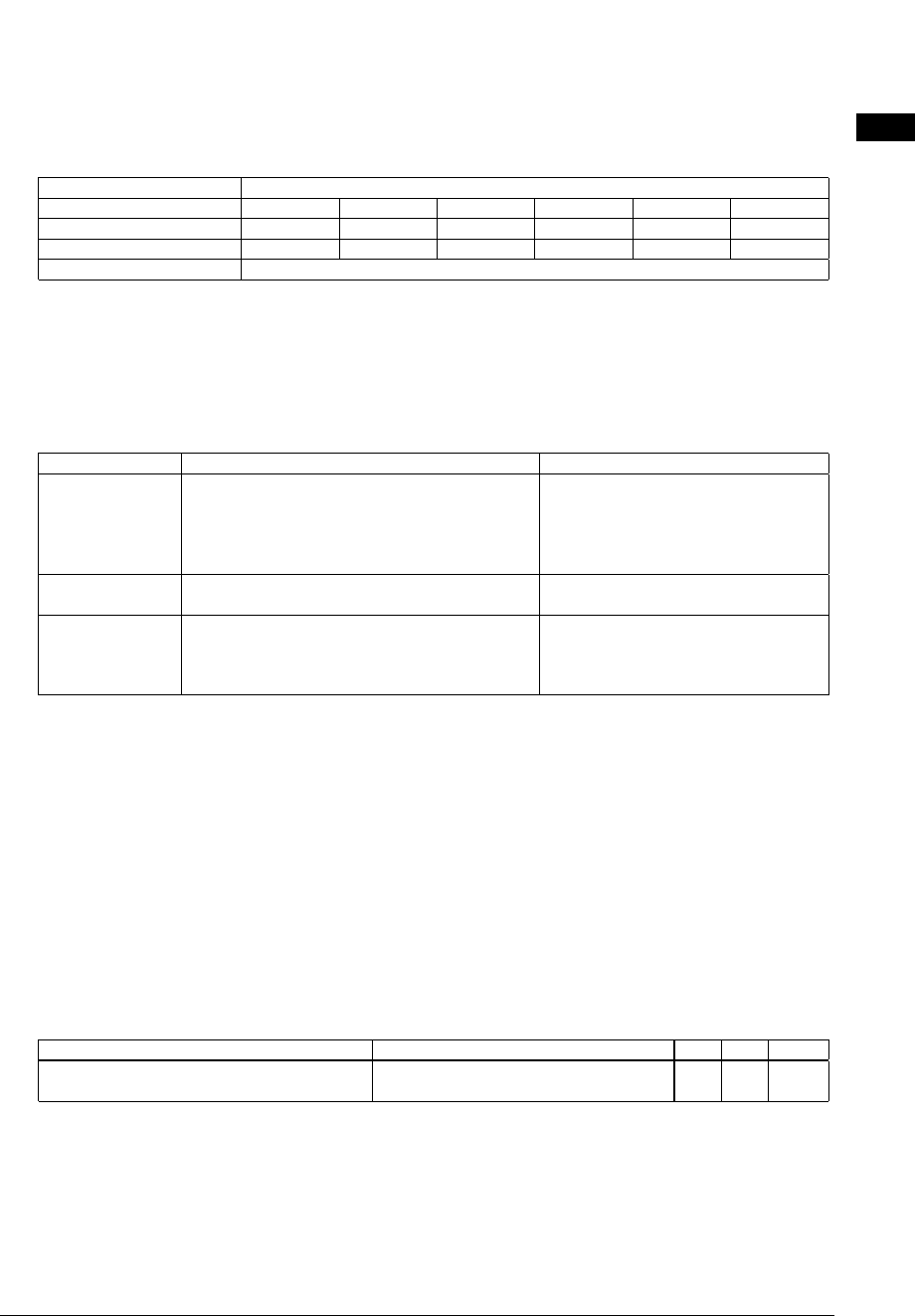

The current consumption of the device varies greatly with the CPU's operation mode, the system clocks used,

and the peripheral circuits operated.

Current consumption low←→high

CPU/BCU SLEEP HALT2 Operating HALT2 HALT(basic) Operating

System clock – OSC1 OSC1 OSC3 OSC3 OSC3

OSC3 oscillation circuit OFF OFF OFF ON ON ON

Prescaler/peripheral circuit STOP RUN

To reduce power consumption of the device, it is important that as many unnecessary circuits as possible be

turned off. In particular, peripheral circuits operating at a fast-clock rate consume a large amount of current,

so design the program so that these circuits are turned off whenever unnecessary.

Power-saving in standby modes

When CPU processing is unnecessary, such as when waiting for an interrupt from key entries or peripheral

circuits, place the device in standby mode to reduce current consumption.

Standby mode Method to enter the mode Circuits/functions stopped

Basic HALT mode Execute the halt instruction after setting HLT2OP

(D3)/Clock option register (0x40190) to "0".

When the #BUSREQ signal is asserted from an

external bus master while SEPD (D1)/Bus control

register (0x4812E) = "1".

CPU (DMA cannot be used.)

HALT2 mode Execute the halt instruction after setting HLT2OP

to "1".

CPU, BCU, bus clock, and DMA

SLEEP mode Execute the slp instruction. CPU, BCU, bus clock, DMA, high-speed

(OSC3) oscillation circuit, prescaler, and

peripheral circuits that use the prescaler

output clocks

HLT2OP (D3)/Clock option register (0x40190) that is used to select a HALT mode is set to "0" (basic HALT

mode) at initial reset.

Notes:•In systems in which DRAM or SDRAM is connected directly to the device, the refresh function is

turned off during HALT2 and SLEEP modes. However, the SDRAM self refresh function can be

used by activating it before the CPU enters HALT2 or SLEEP mode.

•The standby mode is cleared by interrupt generation (except for the basic HALT mode, which is

set using an external bus master). Therefore, before entering standby mode, set the related

registers to allow an interrupt to be used to clear the standby mode to be generated.

•When clearing the standby mode with an interrupt from port input, the interrupt operates as a

level interrupt regardless of the interrupt trigger setting. When edge trigger is set for the interrupt

trigger, attention must be paid to the port level during standby mode.

The low-speed (OSC1) oscillation circuit and clock timer continue operating even during SLEEP mode. If

they are unnecessary, these circuits can also be turned off.

Function Control bit "1" "0" Default

Low-speed (OSC1) oscillation ON/OFF control SOSC1(D0)/

Power control register(0x40180)

ON OFF ON

Switching over the system clocks

Normally, the system is clocked by the high-speed (OSC3) oscillation clock. If high-speed operation is

unnecessary, switch the system clock to the low-speed (OSC1) oscillation clock and turn off the high-speed

(OSC3) oscillation circuit. This helps to reduce current consumption. However, if DRAM is connected

directly to the device, note that the refresh function is also turned off.

Even during operation using the high-speed (OSC3) oscillation clock, power reduction can also be achieved

through the use of a system clock derived from the OSC3 clock by dividing it (1/1, 1/2, 1/4, or 1/8).