II CORE BLOCK: ITC (Interrupt Controller)

S1C33L03 FUNCTION PART EPSON B-II-5-11

A-1

B-II

ITC

HSDMA Invocation

Some interrupt factors can invoke high-speed DMAs (HSDMA).

HSDMA trigger set-up register

The DMA block contains four channel of HSDMA circuit. Each channel allows selection of an interrupt

factor as the trigger. The HSDMA trigger set-up registers are used for this selection.

HSDMA Ch.0: HSD0S[3:0] (D[3:0])/HSDMA Ch.0/1 trigger set-up register (0x40298)

HSDMA Ch.1: HSD1S[3:0] (D[7:4])/HSDMA Ch.0/1 trigger set-up register (0x40298)

HSDMA Ch.2: HSD2S[3:0] (D[3:0])/HSDMA Ch.2/3 trigger set-up register (0x40299)

HSDMA Ch.3: HSD3S[3:0] (D[7:4])/HSDMA Ch.2/3 trigger set-up register (0x40299)

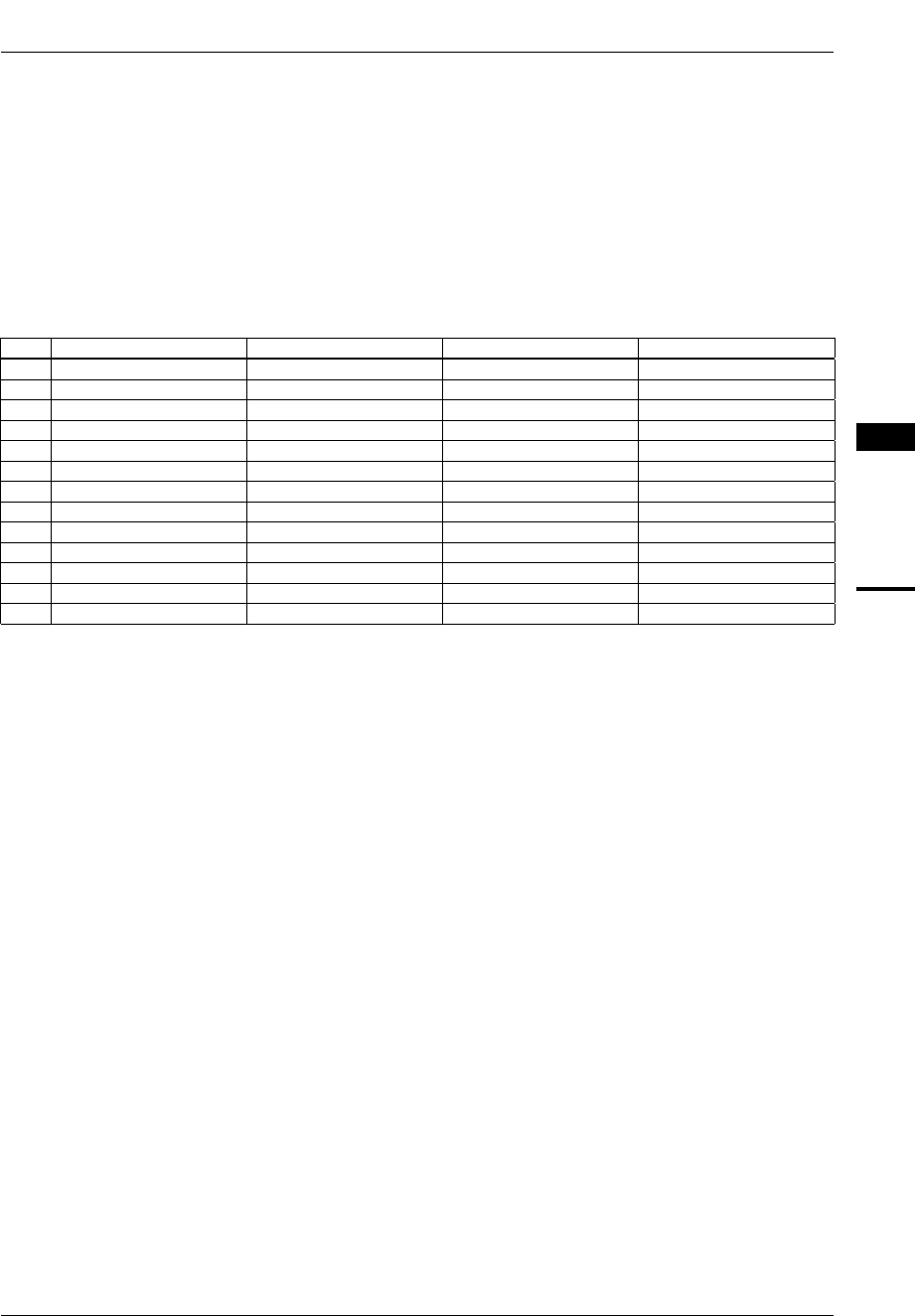

Table 5.2 shows the setting value and the corresponding trigger factor.

Table 5.2 HSDMA Trigger Factor

Value Ch.0 trigger factor Ch.1 trigger factor Ch.2 trigger factor Ch.3 trigger factor

0000 Software trigger Software trigger Software trigger Software trigger

0001 K50 port input (falling edge) K51 port input (falling edge) K53 port input (falling edge) K54 port input (falling edge)

0010 K50 port input (rising edge) K51 port input (rising edge) K53 port input (rising edge) K54 port input (rising edge)

0011 Port 0 input Port 1 input Port 2 input Port 3 input

0100 Port 4 input Port 5 input Port 6 input Port 7 input

0101 8-bit timer 0 underflow 8-bit timer 1 underflow 8-bit timer 2 underflow 8-bit timer 3 underflow

0110 16-bit timer 0 compare B 16-bit timer 1 compare B 16-bit timer 2 compare B 16-bit timer 3 compare B

0111 16-bit timer 0 compare A 16-bit timer 1 compare A 16-bit timer 2 compare A 16-bit timer 3 compare A

1000 16-bit timer 4 compare B 16-bit timer 5 compare B 16-bit timer 4 compare B 16-bit timer 5 compare B

1001 16-bit timer 4 compare A 16-bit timer 5 compare A 16-bit timer 4 compare A 16-bit timer 5 compare A

1010 Serial I/F Ch.0 Rx buffer full Serial I/F Ch.1 Rx buffer full Serial I/F Ch.0 Rx buffer full Serial I/F Ch.1 Rx buffer full

1011 Serial I/F Ch.0 Tx buffer empty Serial I/F Ch.1 Tx buffer empty Serial I/F Ch.0 Tx buffer empty Serial I/F Ch.1 Tx buffer empty

1100 A/D conversion completion A/D conversion completion A/D conversion completion A/D conversion completion

Invoking HSDMA

By selecting an interrupt factor with the HSDMA trigger set-up register, the HSDMA channel is invoked

when the selected interrupt factor occurs. The interrupt control bits (interrupt factor flag, interrupt enable

register, IDMA request register, interrupt priority register) do not affect this invocation.

Since HSDMA does not reset the interrupt factor flag, an interrupt will occur when the DMA transfer is

completed if the interrupt is enabled by ITC.

Before HSDMA can be invoked by the occurrence of an interrupt factor, it is necessary that DMA be enabled

on the HSDMA side by setting the control register for HSDMA transfer.

For details about HSDMA, refer to "HSDMA (High-Speed DMA)".