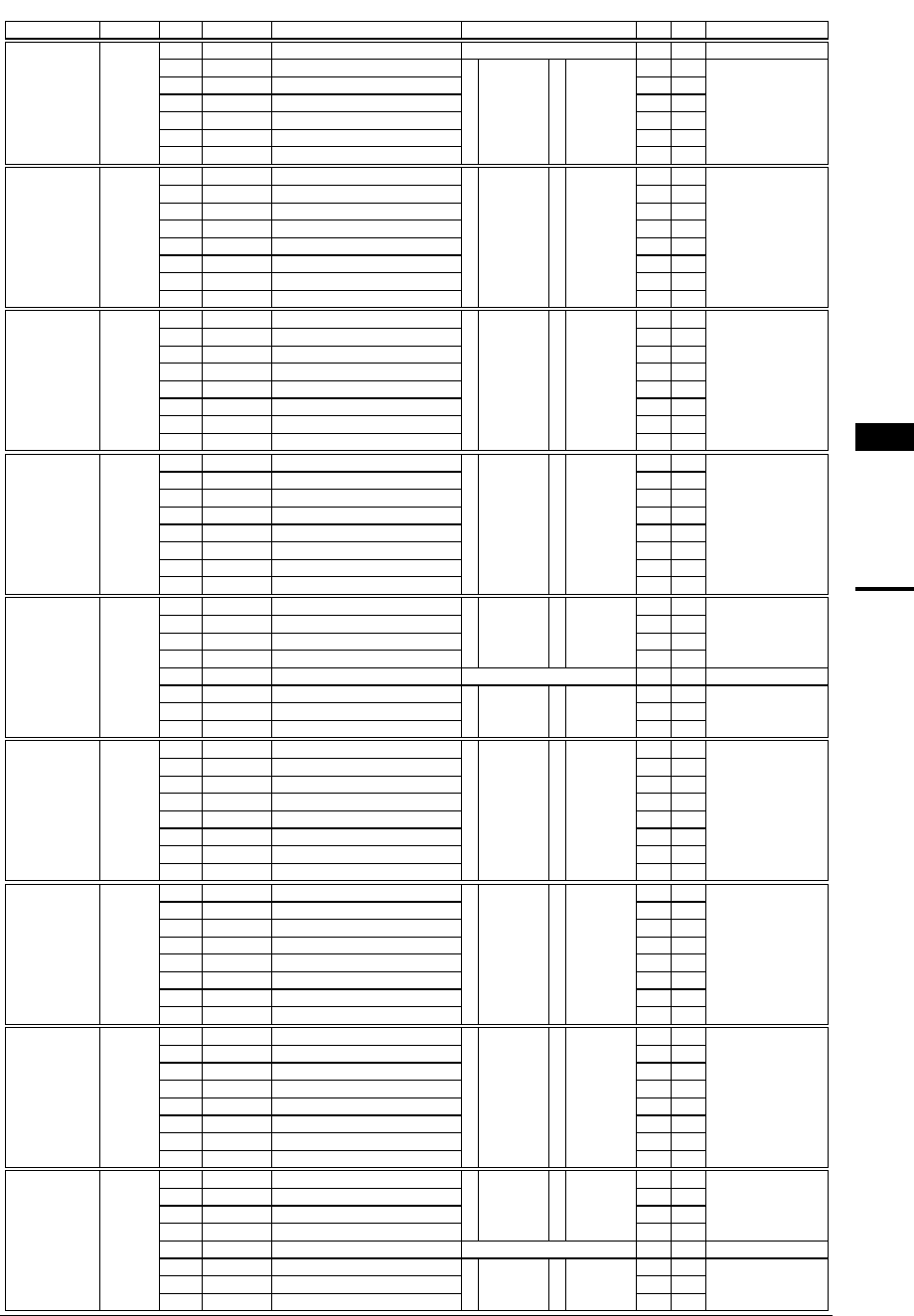

II CORE BLOCK: ITC (Interrupt Controller)

S1C33L03 FUNCTION PART EPSON B-II-5-15

A-1

B-II

ITC

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

FP7

FP6

FP5

FP4

FCTM

FADE

D7–6

D5

D4

D3

D2

D1

D0

reserved

Port input 7

Port input 6

Port input 5

Port input 4

Clock timer

A/D converter

– –

X

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040287

(B)

1 Factor is

generated

0 No factor is

generated

Port input 4–7,

clock timer, A/D

interrupt factor

flag register

R16TC0

R16TU0

RHDM1

RHDM0

RP3

RP2

RP1

RP0

D7

D6

D5

D4

D3

D2

D1

D0

16-bit timer 0 comparison A

16-bit timer 0 comparison B

High-speed DMA Ch.1

High-speed DMA Ch.0

Port input 3

Port input 2

Port input 1

Port input 0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040290

(B)

1 IDMA

request

0 Interrupt

request

Port input 0–3,

high-speed

DMA Ch. 0/1,

16-bit timer 0

IDMA request

register

R16TC4

R16TU4

R16TC3

R16TU3

R16TC2

R16TU2

R16TC1

R16TU1

D7

D6

D5

D4

D3

D2

D1

D0

16-bit timer 4 comparison A

16-bit timer 4 comparison B

16-bit timer 3 comparison A

16-bit timer 3 comparison B

16-bit timer 2 comparison A

16-bit timer 2 comparison B

16-bit timer 1 comparison A

16-bit timer 1 comparison B

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040291

(B)

1 IDMA

request

0 Interrupt

request

16-bit timer 1–4

IDMA request

register

RSTX0

RSRX0

R8TU3

R8TU2

R8TU1

R8TU0

R16TC5

R16TU5

D7

D6

D5

D4

D3

D2

D1

D0

SIF Ch.0 transmit buffer empty

SIF Ch.0 receive buffer full

8-bit timer 3 underflow

8-bit timer 2 underflow

8-bit timer 1 underflow

8-bit timer 0 underflow

16-bit timer 5 comparison A

16-bit timer 5 comparison B

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040292

(B)

1 IDMA

request

0 Interrupt

request

16-bit timer 5,

8-bit timer,

serial I/F Ch.0

IDMA request

register

RP7

RP6

RP5

RP4

–

RADE

RSTX1

RSRX1

D7

D6

D5

D4

D3

D2

D1

D0

Port input 7

Port input 6

Port input 5

Port input 4

reserved

A/D converter

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

0

0

0

0

–

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

0 when being read.

0040293

(B)

1 IDMA

request

0 Interrupt

request

1 IDMA

request

0 Interrupt

request

–

Serial I/F Ch.1,

A/D,

port input 4–7

IDMA request

register

DE16TC0

DE16TU0

DEHDM1

DEHDM0

DEP3

DEP2

DEP1

DEP0

D7

D6

D5

D4

D3

D2

D1

D0

16-bit timer 0 comparison A

16-bit timer 0 comparison B

High-speed DMA Ch.1

High-speed DMA Ch.0

Port input 3

Port input 2

Port input 1

Port input 0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040294

(B)

1 IDMA

enabled

0 IDMA

disabled

Port input 0–3,

high-speed

DMA Ch. 0/1,

16-bit timer 0

IDMA enable

register

DE16TC4

DE16TU4

DE16TC3

DE16TU3

DE16TC2

DE16TU2

DE16TC1

DE16TU1

D7

D6

D5

D4

D3

D2

D1

D0

16-bit timer 4 comparison A

16-bit timer 4 comparison B

16-bit timer 3 comparison A

16-bit timer 3 comparison B

16-bit timer 2 comparison A

16-bit timer 2 comparison B

16-bit timer 1 comparison A

16-bit timer 1 comparison B

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040295

(B)

1 IDMA

enabled

0 IDMA

disabled

16-bit timer 1–4

IDMA enable

register

DESTX0

DESRX0

DE8TU3

DE8TU2

DE8TU1

DE8TU0

DE16TC5

DE16TU5

D7

D6

D5

D4

D3

D2

D1

D0

SIF Ch.0 transmit buffer empty

SIF Ch.0 receive buffer full

8-bit timer 3 underflow

8-bit timer 2 underflow

8-bit timer 1 underflow

8-bit timer 0 underflow

16-bit timer 5 comparison A

16-bit timer 5 comparison B

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040296

(B)

1 IDMA

enabled

0 IDMA

disabled

16-bit timer 5,

8-bit timer,

serial I/F Ch.0

IDMA enable

register

DEP7

DEP6

DEP5

DEP4

–

DEADE

DESTX1

DESRX1

D7

D6

D5

D4

D3

D2

D1

D0

Port input 7

Port input 6

Port input 5

Port input 4

reserved

A/D converter

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

0

0

0

0

–

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

0 when being read.

0040297

(B)

1 IDMA

enabled

0 IDMA

disabled

1 IDMA

enabled

0 IDMA

disabled

–

Serial I/F Ch.1,

A/D,

port input 4–7

IDMA enable

register