VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

B-VI-2-22 EPSON S1C33L03 FUNCTION PART

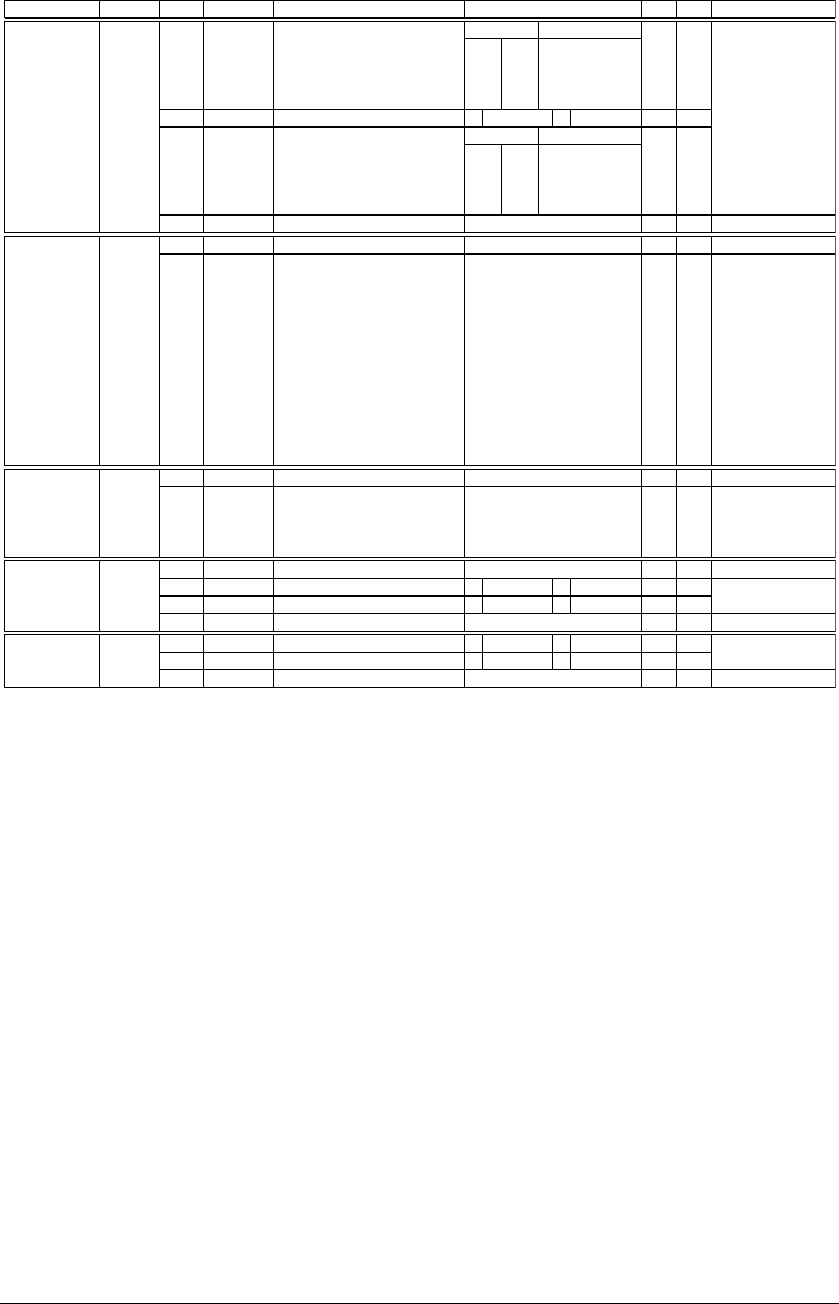

NameAddressRegister name Bit Function Setting Init. R/W Remarks

SDRTRCD1

SDRTRCD0

SDRTRSC

SDRTRRD1

SDRTRRD0

–

D7–6

D5

D4–3

D2–0

SDRAM t

RCD

spec

SDRAM t

RSC

spec

SDRAM t

RRD

spec

reserved

0

0

0

0

0

–

R/W

R/W

R/W

–

0 when being read.

039FFC5

(B)

SDRAM

timing set-up

register 2

1

1

0

0

1

0

1

0

SDRTRCD[1:0]

Number of clocks

3

2

1

4

1

1

0

0

1

0

1

0

SDRTRRD[1:0]

Number of clocks

3

2

1

4

–

1 1 clock 0 2 clocks

–

SDRARFC11

SDRARFC10

SDRARFC9

SDRARFC8

SDRARFC7

SDRARFC6

SDRARFC5

SDRARFC4

SDRARFC3

SDRARFC2

SDRARFC1

SDRARFC0

DF–C

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

SDRAM auto refresh count [11:0]

–

1

1

1

1

1

1

1

1

1

1

1

1

–

R/W

0 when being read.039FFC6

(HW)

SDRAM

auto refresh

count register

0 to 4096

–

–

SDRSRFC3

SDRSRFC2

SDRSRFC1

SDRSRFC0

D7–4

D3

D2

D1

D0

reserved

SDRAM self refresh count [3:0]

–

1

1

1

1

–

R/W

0 when being read.

This register must

not be set less than

"0x02".

039FFC8

(B)

SDRAM

self refresh

count register

2 to 15

–

–

––

SDRSZ

SDRBI

–

D7

D6

D5

D4–0

reserved

SDRAM data path bit width

SDRAM bank interleaved access

reserved

–

0

0

–

–

R/W

R/W

–

0 when being read.

0 when being read.

039FFC9

(B)

1 8 bits 0 16 bits

1 Interleaved 0 One bank

SDRAM

advanced

control

register

–

SDRMRS

SDRSRM

–

D7

D6

D5–0

SDRAM mode register set flag

SDRAM current refresh mode

reserved

1

1

–

R

R

–

0 when being read.

039FFCA

(B)

1 Not finished 0 Done

1

Auto refresh

0 Self refresh

SDRAM

status register

Note:Do not access addresses 0x039FFCB to 0x039FFCD, because they are reserved for testing the

SDRAM controller.