VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

S1C33L03 FUNCTION PART EPSON B-VI-2-23

A-1

B-VI

SDRAM

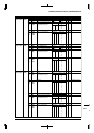

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

A14DRA

A13DRA

A14SZ

A14DF1

A14DF0

–

A14WT2

A14WT1

A14WT0

DF–9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Area 14 DRAM selection

Area 13 DRAM selection

Areas 14–13 device size selection

Areas 14–13

output disable delay time

reserved

Areas 14–13 wait control

–

–

1 Used 0 Not used

1 Used 0 Not used

1 8 bits 0 16 bits

–

0

0

0

1

1

–

1

1

1

–

R/W

R/W

R/W

R/W

–

R/W

0 when being read.

0 when being read.

0048122

(HW)

1

1

0

0

1

0

1

0

A14DF[1:0] Number of cycles

3.5

2.5

1.5

0.5

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

A14WT[2:0] Wait cycles

7

6

5

4

3

2

1

0

Areas 14–13

set-up register

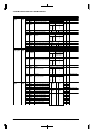

–

A8DRA

A7DRA

A8SZ

A8DF1

A8DF0

–

A8WT2

A8WT1

A8WT0

DF–9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Area 8 DRAM selection

Area 7 DRAM selection

Areas 8–7 device size selection

Areas 8–7

output disable delay time

reserved

Areas 8–7 wait control

–

–

1 Used 0 Not used

1 Used 0 Not used

1 8 bits 0 16 bits

–

0

0

0

1

1

–

1

1

1

–

R/W

R/W

R/W

R/W

–

R/W

0 when being read.

0 when being read.

0048128

(HW)

Areas 8–7

set-up register

1

1

0

0

1

0

1

0

A8DF[1:0] Number of cycles

3.5

2.5

1.5

0.5

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

A8WT[2:0] Wait cycles

7

6

5

4

3

2

1

0

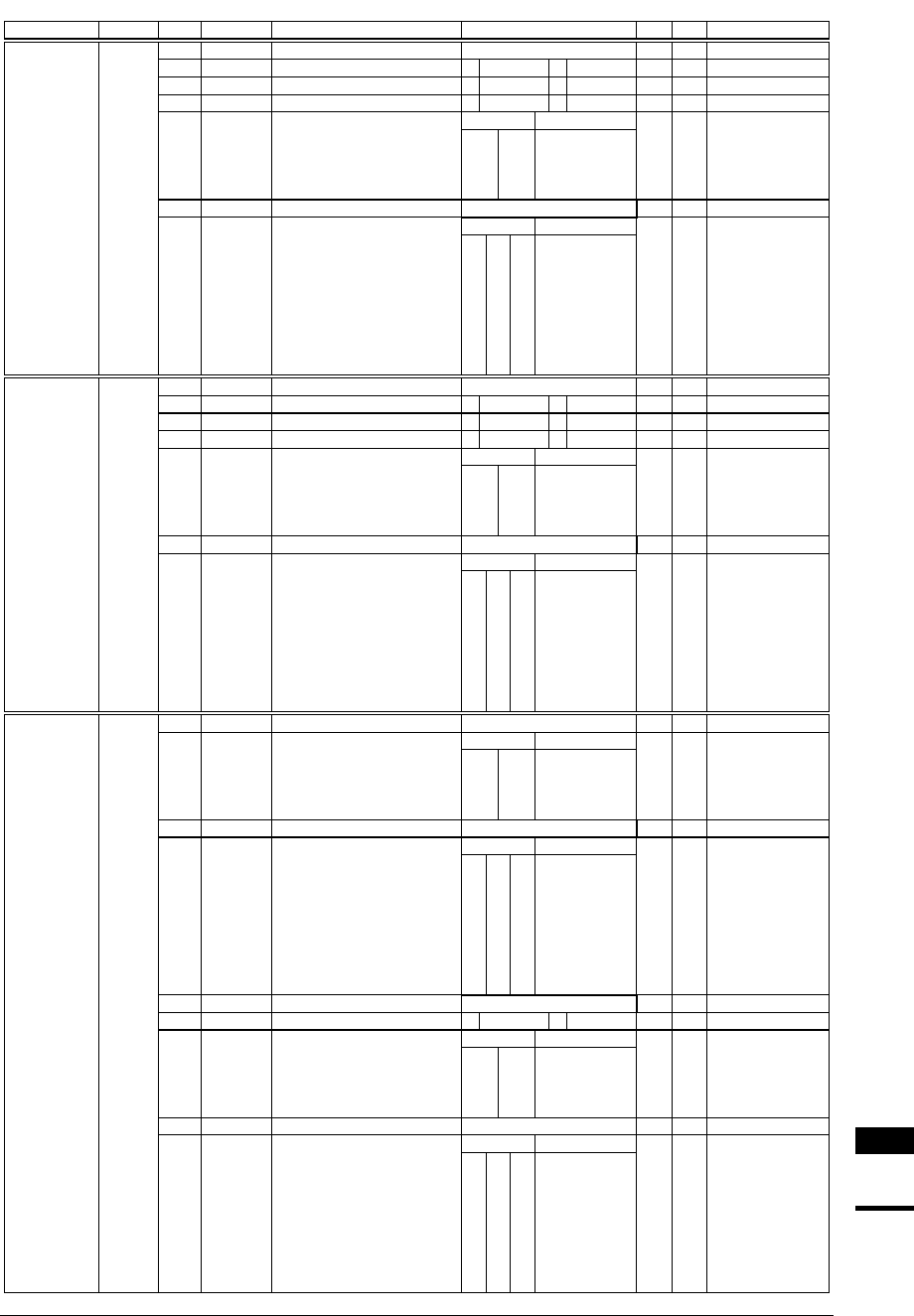

–

A6DF1

A6DF0

–

A6WT2

A6WT1

A6WT0

–

A5SZ

A5DF1

A5DF0

–

A5WT2

A5WT1

A5WT0

DF–E

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Area 6

output disable delay time

reserved

Area 6 wait control

reserved

Areas 5–4 device size selection

Areas 5–4

output disable delay time

reserved

Areas 5–4 wait control

–

–

–

1 8 bits 0 16 bits

–

1

1

–

1

1

1

–

0

1

1

–

1

1

1

–

R/W

–

R/W

–

R/W

R/W

–

R/W

0 when being read.

0 when being read.

0 when being read.

0 when being read.

004812A

(HW)

Areas 6–4

set-up register

1

1

0

0

1

0

1

0

A6DF[1:0] Number of cycles

3.5

2.5

1.5

0.5

1

1

0

0

1

0

1

0

A5DF[1:0] Number of cycles

3.5

2.5

1.5

0.5

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

A6WT[2:0] Wait cycles

7

6

5

4

3

2

1

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

A5WT[2:0] Wait cycles

7

6

5

4

3

2

1

0