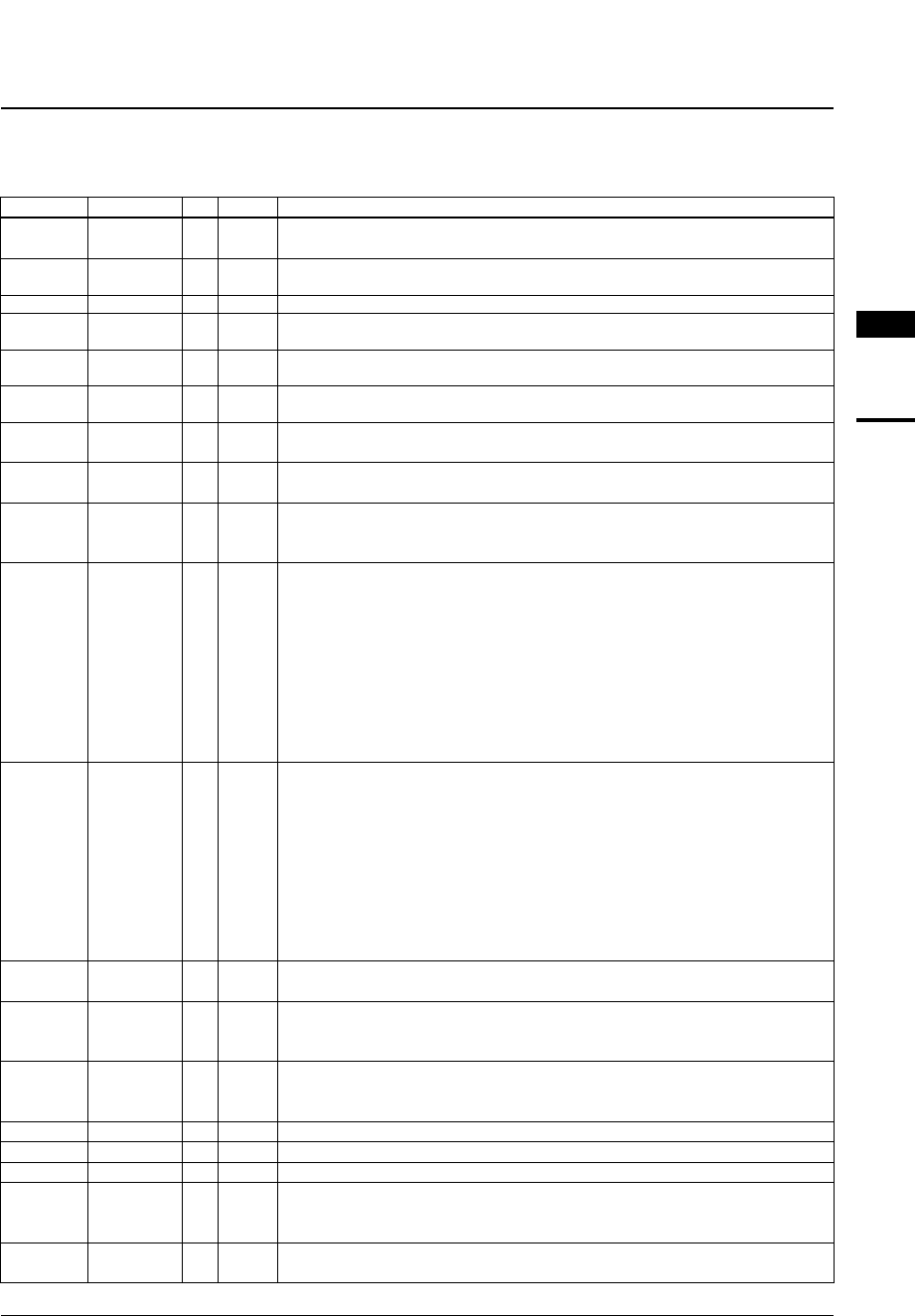

I OUTLINE: LIST OF PINS

S1C33L03 FUNCTION PART EPSON B-I-3-1

A-1

B-I

Pin

I-3 LIST OF PINS

List of External I/O Pins

The following lists the external I/O pins of the C33 Core Block, Peripheral Block and LCD Controller Block. Note

that some pins are listed in two or more tables.

Table 3.1 List of Pins for External Bus Interface Signals

Pin name Pin No. I/O Pull-up Function

A0

#BSL

85 O – A0: Address bus (A0) when SBUSST(D3/0x4812E) = "0" (default)

#BSL: Bus strobe (low byte) signal when SBUSST(D3/0x4812E) = "1"

A[10:1]

SDA[9:0]

85–90,92–96 O

–

A[10:1]: Address bus (A1–A10)

SDA[9:0]: SDRAM address bus (SDA0–SDA9)

A11 97 O – Address bus (A11)

A[13:12]

SDA[12:11]

99,100 O – A[13:12]: Address bus (A12–A13)

SDA[12:11]: SDRAM address bus (SDA11–SDA12)

A[15:14]

SDBA[1:0]

101,102 O – A[15:14]: Address bus (A14–A15)

SDBA[1:0]: SDRAM bank select (SDBA0–SDBA1)

A[23:16] 103,104,

106–111

O–Address bus (A16–A23)

D[15:0] 46–50,52–58,

60–63

I/O – Data bus (D0–D15)

#CE10EX

#CE9&10EX

137 O – Area 10 chip enable for external memory

* When CEFUNC[1:0] = "1x", this pin outputs #CE9+#CE10EX signal.

#CE9

#CE17

#CE17&18

131 O – #CE9: Area 9 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "00" (default)

#CE17: Area 17 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "01"

* When CEFUNC[1:0] = "1x", this pin outputs #CE17+#CE18 signal.

#CE8

#RAS1

#CE14

#RAS3

#SDCE1

64 O – #CE8: Area 8 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "00",

A8DRA(D8/0x48128) = "0" and SDRPC1(D2/0x39FFC0) = "0" (default)

#RAS1: Area 8 DRAM row strobe when CEFUNC[1:0](D[A:9]/0x48130) = "00",

A8DRA(D8/0x48128) = "1" and SDRPC1(D2/0x39FFC0) = "0"

#CE14: Area 14 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "01" or "1x",

A14DRA(D8/0x48122) = "0" and SDRPC1(D2/0x39FFC0) = "0"

#RAS3: Area 14 DRAM row strobe when CEFUNC[1:0](D[A:9]/0x48130) = "01" or

"1x", A14DRA(D8/0x48122) = "1" and SDRPC1(D2/0x39FFC0) = "0"

#SDCE1: SDRAM chip enable 1 when SDRPC1(D2/0x39FFC0) = "1" and

SDRENA(D7/0x39FFC1) = "1"

#CE7

#RAS0

#CE13

#RAS2

#SDCE0

65 O – #CE7: Area 7 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "00",

A7DRA(D7/0x48128) = "0" and SDRPC0(D3/0x39FFC0) = "0" (default)

#RAS0: Area 7 DRAM row strobe when CEFUNC[1:0](D[A:9]/0x48130) = "00",

A7DRA(D7/0x48128) = "1" and SDRPC0(D3/0x39FFC0) = "0"

#CE13: Area 13 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "01" or "1x",

A13DRA(D7/0x48122) = "0" and SDRPC0(D3/0x39FFC0) = "0"

#RAS2: Area 13 DRAM row strobe when CEFUNC[1:0](D[A:9]/0x48130) = "01" or

"1x", A13DRA(D7/0x48122) = "1" and SDRPC0(D3/0x39FFC0) = "0"

#SDCE0: SDRAM chip enable 0 when SDRPC0(D3/0x39FFC0) = "1" and

SDRENA(D7/0x39FFC1) = "1"

#CE6

#CE7&8

138 O – Area 6 chip enable

* When CEFUNC[1:0] = "1x", this pin outputs #CE7+#CE8 signal.

#CE5

#CE15

#CE15&16

133 O – #CE5: Area 5 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "00" (default)

#CE15: Area 15 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "01"

* When CEFUNC[1:0] = "1x", this pin outputs #CE15+#CE16 signal.

#CE4

#CE11

#CE11&12

139 O – #CE4: Area 4 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "00" (default)

#CE11: Area 11 chip enable when CEFUNC[1:0](D[A:9]/0x48130) = "01"

* When CEFUNC[1:0] = "1x", this pin outputs #CE11+#CE12 signal.

#CE3 135 O – Area 3 chip enable

#RD 44 O – Read signal

#EMEMRD 126 O – Read signal for internal ROM emulation memory

#WRL

#WR

#WE

43 O – #WRL: Write (low byte) signal when SBUSST(D3/0x4812E) = "0" (default)

#WR: Write signal when SBUSST(D3/0x4812E) = "1"

#WE: DRAM write signal

#WRH

#BSH

42 O – #WRH: Write (high byte) signal when SBUSST(D3/0x4812E) = "0" (default)

#BSH: Bus strobe (high byte) signal when SBUSST(D3/0x4812E) = "1"