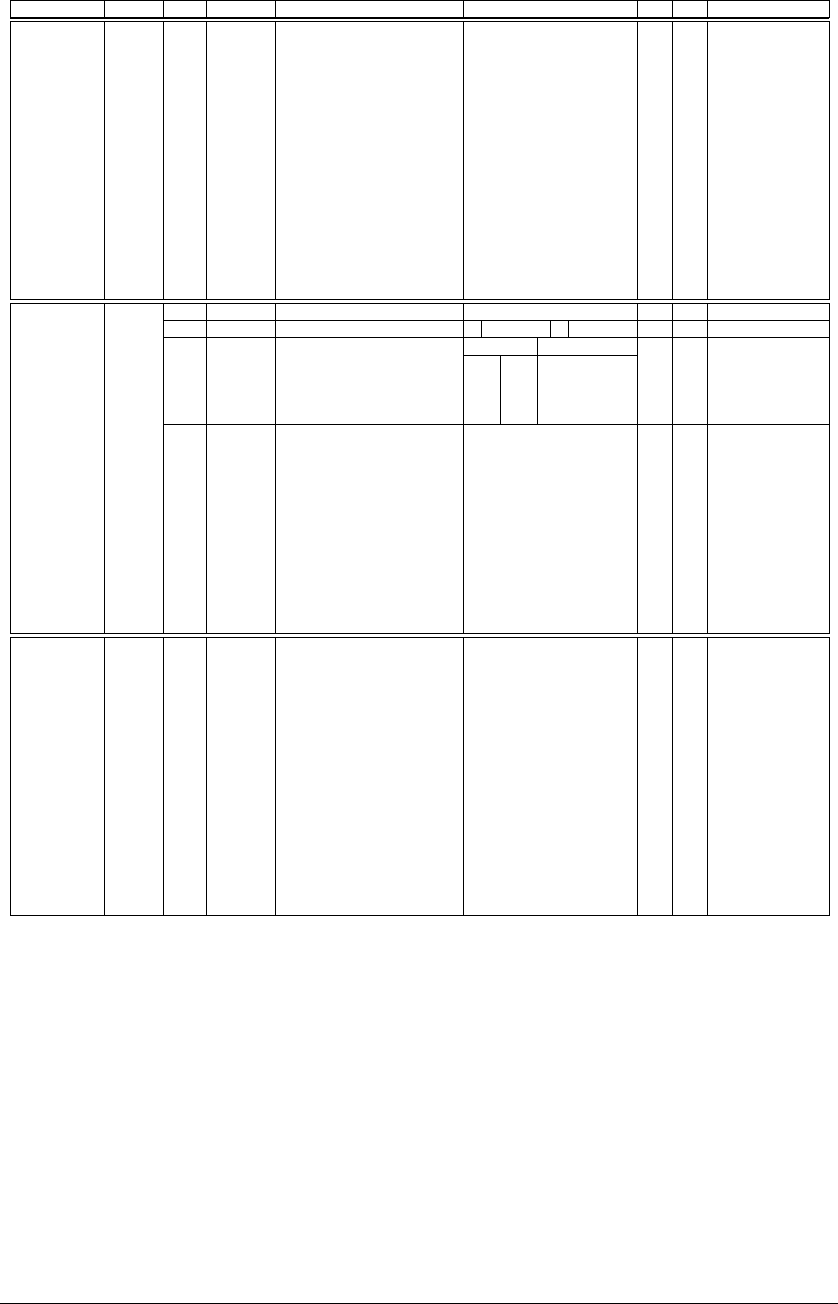

V DMA BLOCK: HSDMA (High-Speed DMA)

B-V-2-24 EPSON S1C33L03 FUNCTION PART

NameAddressRegister name Bit Function Setting Init. R/W Remarks

S2ADRL15

S2ADRL14

S2ADRL13

S2ADRL12

S2ADRL11

S2ADRL10

S2ADRL9

S2ADRL8

S2ADRL7

S2ADRL6

S2ADRL5

S2ADRL4

S2ADRL3

S2ADRL2

S2ADRL1

S2ADRL0

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

D) Ch.2 source address[15:0]

S) Ch.2 memory address[15:0]

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

R/W0048244

(HW)

High-speed

DMA Ch.2

low-order

source address

set-up register

Note:

D) Dual address

mode

S) Single

address

mode

–

DATSIZE2

S2IN1

S2IN0

S2ADRH11

S2ADRH10

S2ADRH9

S2ADRH8

S2ADRH7

S2ADRH6

S2ADRH5

S2ADRH4

S2ADRH3

S2ADRH2

S2ADRH1

S2ADRH0

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Ch.2 transfer data size

D) Ch.2 source address control

S) Ch.2 memory address control

D) Ch.2 source address[27:16]

S) Ch.2 memory address[27:16]

–

0

0

0

X

X

X

X

X

X

X

X

X

X

X

X

–

R/W

R/W

R/W

0048246

(HW)

1 Half word 0 Byte

High-speed

DMA Ch.2

high-order

source address

set-up register

Note:

D) Dual address

mode

S) Single

address

mode

1

1

0

0

1

0

1

0

S2IN[1:0] Inc/dec

Inc.(no init)

Inc.(init)

Dec.(no init)

Fixed

–

D2ADRL15

D2ADRL14

D2ADRL13

D2ADRL12

D2ADRL11

D2ADRL10

D2ADRL9

D2ADRL8

D2ADRL7

D2ADRL6

D2ADRL5

D2ADRL4

D2ADRL3

D2ADRL2

D2ADRL1

D2ADRL0

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

D) Ch.2 destination address[15:0]

S) Invalid

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

R/W0048248

(HW)

High-speed

DMA Ch.2

low-order

destination

address set-up

register

Note:

D) Dual address

mode

S) Single

address

mode