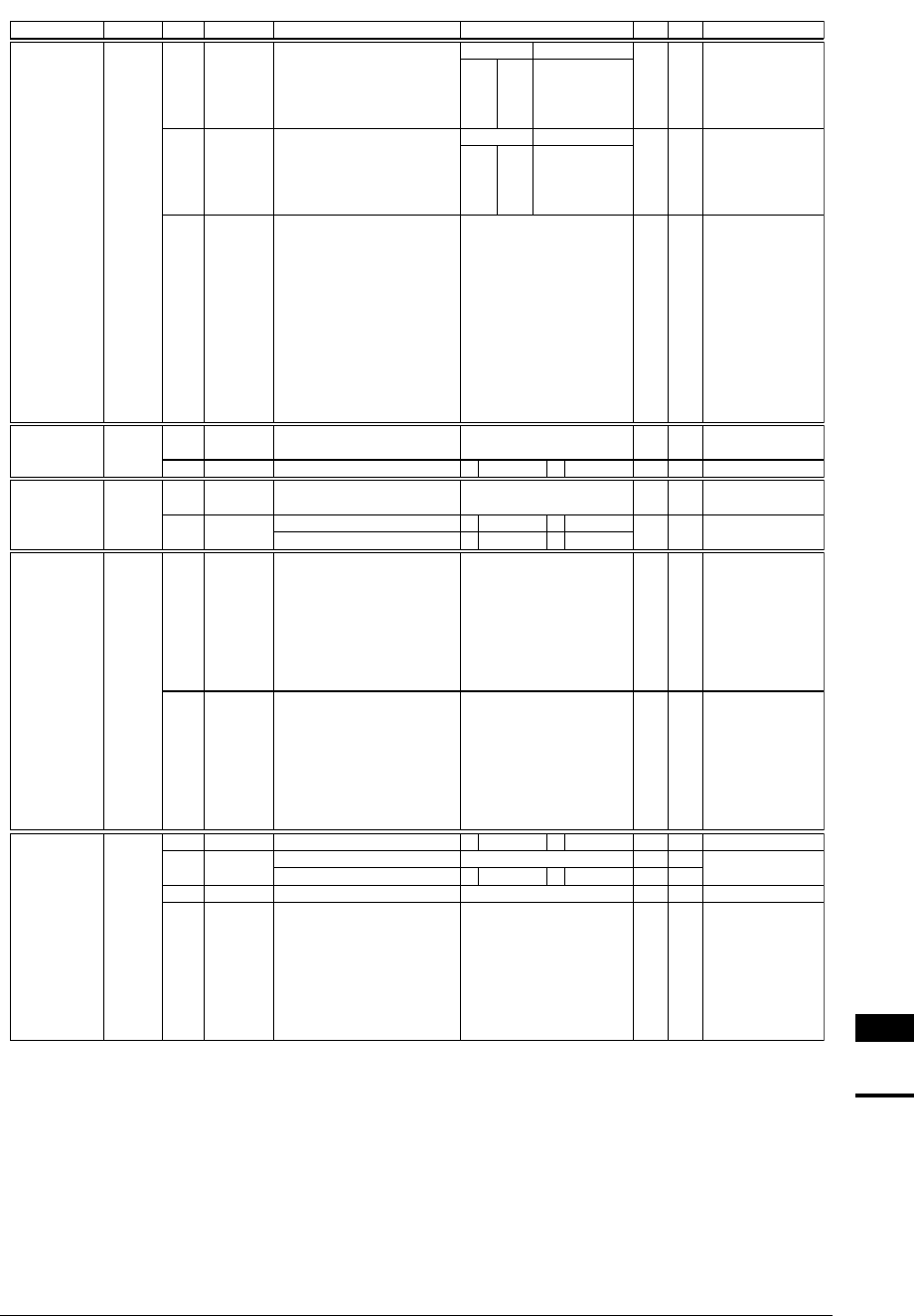

V DMA BLOCK: HSDMA (High-Speed DMA)

S1C33L03 FUNCTION PART EPSON B-V-2-23

A-1

B-V

HSDMA

NameAddressRegister name Bit Function Setting Init. R/W Remarks

D1MOD1

D1MOD0

D1IN1

D1IN0

D1ADRH11

D1ADRH10

D1ADRH9

D1ADRH8

D1ADRH7

D1ADRH6

D1ADRH5

D1ADRH4

D1ADRH3

D1ADRH2

D1ADRH1

D1ADRH0

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Ch.1 transfer mode

D) Ch.1 destination address

control

S) Invalid

D) Ch.1 destination

address[27:16]

S) Invalid

0

0

0

0

X

X

X

X

X

X

X

X

X

X

X

X

R/W

R/W

R/W

004823A

(HW)

High-speed

DMA Ch.1

high-order

destination

address set-up

register

Note:

D) Dual address

mode

S) Single

address

mode

1

1

0

0

1

0

1

0

D1MOD[1:0] Mode

Invalid

Block

Successive

Single

1

1

0

0

1

0

1

0

D1IN[1:0] Inc/dec

Inc.(no init)

Inc.(init)

Dec.(no init)

Fixed

––

HS1_EN

DF–1

D0

reserved

Ch.1 enable

1 Enable 0 Disable

–

0

–

R/W

Undefined in read.004823C

(HW)

High-speed

DMA Ch.1

enable register

––

HS1_TF

DF–1

D0

reserved

Ch.1 trigger flag clear (writing)

Ch.1 trigger flag status (reading)

1 Clear 0

No operation

1 Set 0 Cleared

–

0

–

R/W

Undefined in read.004823E

(HW)

High-speed

DMA Ch.1

trigger flag

register

TC2_L7

TC2_L6

TC2_L5

TC2_L4

TC2_L3

TC2_L2

TC2_L1

TC2_L0

BLKLEN27

BLKLEN26

BLKLEN25

BLKLEN24

BLKLEN23

BLKLEN22

BLKLEN21

BLKLEN20

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Ch.2 transfer c

ounter[7:0]

(block transfer mode)

Ch.2 transfer counter[15:8]

(single/successive transfer mode)

Ch.2 block length

(block transfer mode)

Ch.2 transfer counter[7:0]

(single/successive transfer mode)

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

R/W

R/W

0048240

(HW)

High-speed

DMA Ch.2

transfer

counter

register

–

–

DUALM2

D2DIR

–

TC2_H7

TC2_H6

TC2_H5

TC2_H4

TC2_H3

TC2_H2

TC2_H1

TC2_H0

DF

DE

DD–8

D7

D6

D5

D4

D3

D2

D1

D0

Ch.2 address mode selection

D) Invalid

S) Ch.2 transfer direction control

reserved

Ch.2 transfer counter[15:8]

(block transfer mode)

Ch.2 transfer counter[23:16]

(single/successive transfer mode)

1 Dual addr 0 Single addr

1

Memory WR

0

Memory RD

0

–

0

–

X

X

X

X

X

X

X

X

R/W

–

R/W

–

R/W

Undefined in read.

0048242

(HW)

High-speed

DMA Ch.2

control register

Note:

D) Dual address

mode

S) Single

address

mode