VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

B-VI-2-18 EPSON S1C33L03 FUNCTION PART

Self refresh

Self-refresh uses the SDRAM’s self-refresh function and does not require clock pulses during the refresh

period, thus helping to reduce the chip’s power consumption. This self-refresh function is also used for data

retention during power-down mode.

To cause the SDRAM to be self-refreshed, set the SDRSRF (D5)/SDRAM control register (0x39FFC1) to "1".

This enables the SDRAM controller to send the self-refresh command (which sets the SDCKE output to low)

to the SDRAM. The command is actually sent a certain time after accessing or auto-refreshing the SDRAM,

so the SDRAM controller contains a 4-bit self-refresh counter to count this time. The counter counts on

SDRAM clock (SD_CLK) edges, and when the designated count is reached, the SDRAM controller sends the

refresh command to the SDRAM. When an SDRAM access or auto-refresh command is issued, the counter is

reset and starts counting again. The designated value for the counter can be specified in a range of 2 to 15 by

using the SDRSRFC[3:0] (D[3:0])/SDRAM self refresh count register (0x39FFC8). Always set the SDRAM

self refresh count register to 2 or more. If it is set to less than 2, the SDRAM cannot exit self-refresh mode.

When an SDRAM access occurs during self-refresh mode, SDCKE is returned high and the SDRAM is taken

out of self-refresh mode.

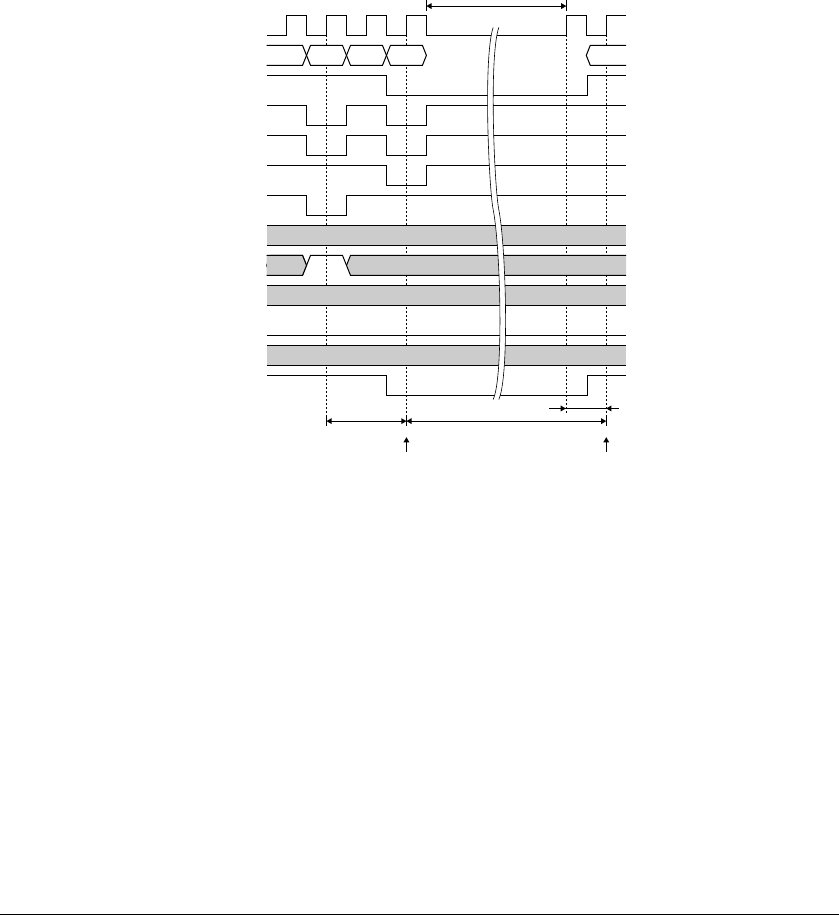

BCLK

Command

SDCKE

#SDCEx

#SDRAS

#SDCAS

#SDWE

SDBA[1:0]

SDA[10]

SDA[12:11, 9:0]

LDQM/HDQM

DQ[15:0]

SDRSRM

SELFNOP

L

NOPPALL NOP

Self refresh mode

Enters self refresh mode

1 clock cycle

Exits self refresh mode

t

RP

The SDRAM clock stops when SDRCLK = "0".

Figure 2.16 Self Refresh

During self-refresh (while SDCKE = low), the SDRSRM (D6)/SDRAM status register (0x39FFCA) remains

"0". Therefore, it is possible to determine whether or not self-refresh is in operation by reading this status

register.

Furthermore, SDRAM clock output during self-refresh can be turned off in order to reduce the chip’s power

consumption by setting the SDRCLK (D3)/SDRAM control register (0x39FFC1) to "0".