II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-38 EPSON S1C33L03 FUNCTION PART

A18SZ:Areas 18–17 device size selection (DE) / Areas 18–15 set-up register (0x48120)

A16SZ:Areas 16–15 device size selection (D6) / Areas 18–15 set-up register (0x48120)

A14SZ:Areas 14–13 device size selection (D6) / Areas 14–13 set-up register (0x48122)

A12SZ:Areas 12–11 device size selection (D6) / Areas 12–11 set-up register (0x48124)

A10SZ:Areas 10–9 device size selection (D6) / Areas 10–9 set-up register (0x48126)

A8SZ:Areas 8–7 device size selection (D6) / Areas 8–7 set-up register (0x48128)

A5SZ:Areas 5–4 device size selection (D6) / Areas 6–4 set-up register (0x4812A)

Select the size of the device connected to each area.

Write "1": 8 bits

Write "0": 16 bits

Read: Valid

A device size can be selected for every two areas. An 8-bit size is selected by writing "1" to AxxSZ and a 16-bit

size is selected by writing "0" to AxxSZ. Area 6 has its first half (0x300000 through 0x37FFFF) fixed to an 8-bit

device and the last half (0x380000 through 0x3FFFFF) fixed to a 16-bit device.

At cold start, these bits are set to "0" (16 bits). At hot start, these bits retain their status before being initialized.

A18DF1–A18DF0:

Areas 18–17 output disable delay time (D[D:C]) / Areas 18–15 set-up register (0x48120)

A16DF1–A16DF0: Areas 16–15 output disable delay time (D[5:4]) / Areas 18–15 set-up register (0x48120)

A14DF1–A14DF0: Areas 14–13 output disable delay time (D[5:4]) / Areas 14–13 set-up register (0x48122)

A12DF1–A12DF0: Areas 12–11 output disable delay time (D[5:4]) / Areas 12–11 set-up register (0x48124)

A10DF1–A10DF0: Areas 10–9 output disable delay time (D[5:4]) / Areas 10–9 set-up register (0x48126)

A8DF1–A8DF0: Areas 8–7 output disable delay time (D[5:4]) / Areas 8–7 set-up register (0x48128)

A6DF1–A6DF0: Area 6 output disable delay time (D[D:C]) / Areas 6–4 set-up register (0x4812A)

A5DF1–A5DF0: Areas 5–4 output disable delay time (D[5:4]) / Areas 6–4 set-up register (0x4812A)

Set the output-disable delay time.

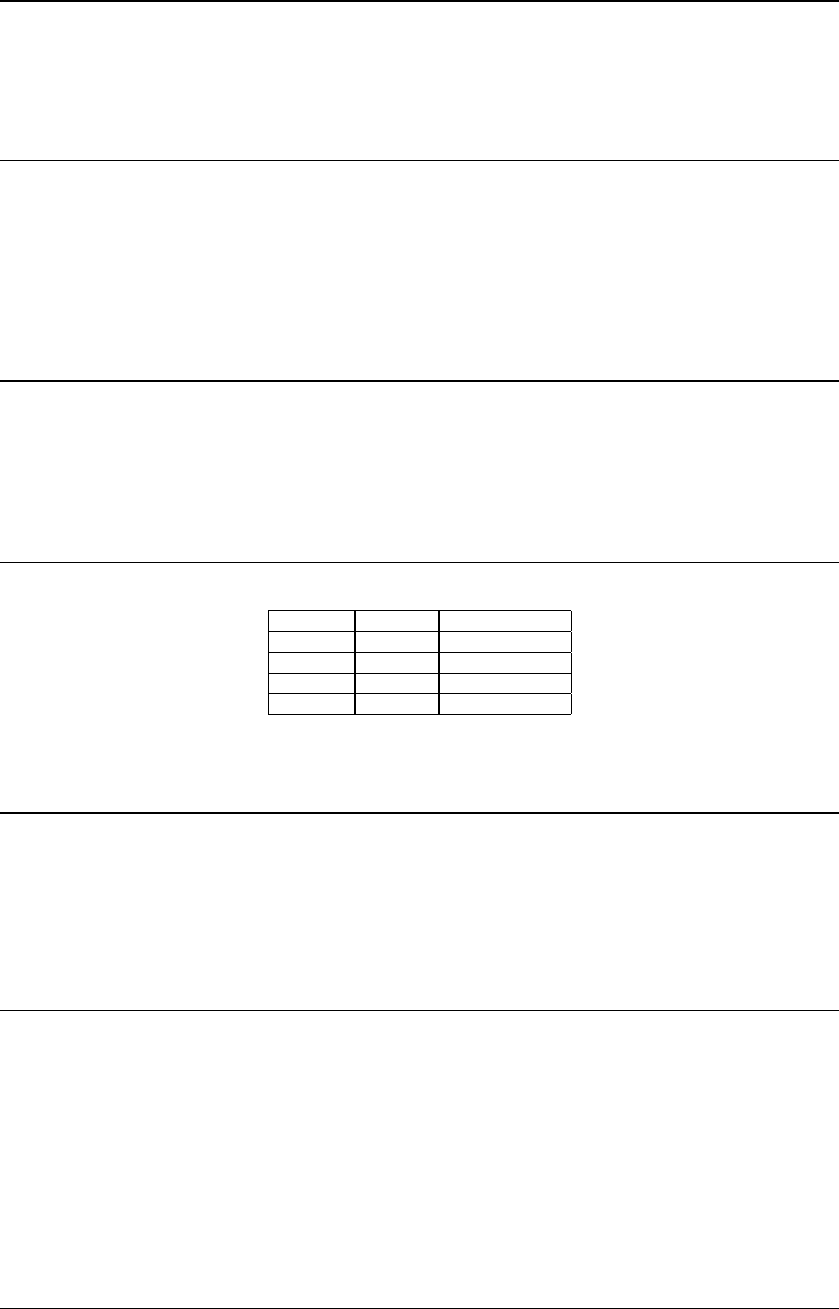

Table 4.24 Output Disable Delay Time

AxxDF1 AxxDF0 Delay time

113.5 cycles

102.5 cycles

011.5 cycles

000.5 cycles

When using a device that has a long output-disable time, set a delay time to ensure that no contention for the data

bus occurs during the bus operation immediately after a device is read.

At cold start, these bits are set to "11" (3.5 cycles). At hot start, the bits retain their status before being initialized.

A18WT2–A18WT0:Areas 18–17 wait control (D[A:8]) / Areas 18–15 set-up register (0x48120)

A16WT2–A16WT0:Areas 16–15 wait control (D[2:0]) / Areas 18–15 set-up register (0x48120)

A14WT2–A14WT0:Areas 14–13 wait control (D[2:0]) / Areas 14–13 set-up register (0x48122)

A12WT2–A12WT0:Areas 12–11 wait control (D[2:0]) / Areas 12–11 set-up register (0x48124)

A10WT2–A10WT0:Areas 10–9 wait control (D[2:0]) / Areas 10–9 set-up register (0x48126)

A8WT2–A8WT0:Areas 8–7 wait control (D[2:0]) / Areas 8–7 set-up register (0x48128)

A6WT2–A6WT0:Area 6 wait control (D[A:8]) / Areas 6–4 set-up register (0x4812A)

A5WT2–A5WT0:Areas 5–4 wait control (D[2:0]) / Areas 6–4 set-up register (0x4812A)

Set the number of wait cycles to be inserted when accessing an SRAM device.

The values 0 through 7 written to the control bits equal the number of wait cycles inserted.

Note that the write cycle consists of a minimum of two cycles, so that a writing 0 or 1 is invalid.

When an SRAM device is connected, wait cycles derived via the #WAIT pin can also be inserted. In this case too,

the wait cycles set by AxxWT are valid.

The DRAM read/write cycles do not have wait cycles inserted that are set by AxxWT or derived from the #WAIT

pin.

The burst read cycle of a burst ROM (except for the first access) also does not have any wait cycle inserted. The

first read cycle of a burst ROM and the write cycle to the burst ROM area have wait cycles inserted that are set by

AxxWT. Wait cycles derived from the #WAIT pin also can be inserted in the cycle for writing to the burst ROM

area.

At cold start, these bits are set to "111" (7 cycles). At hot start, the bits retain their status before being initialized.