VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

S1C33L03 FUNCTION PART EPSON B-VI-2-5

A-1

B-VI

SDRAM

SDRAM Controller Configuration

Setting PLL

When using the SDRAM controller, always enable the PLL. Refer to "PLL" in Section II-6, "CLG (Clock

Generator)", for setting the PLL.

The following shows the operating range of the SDRAM controller when the PLL is enabled.

#X2SPD pin = "1" (x1 speed mode): 25 MHz max. (CPU operating frequency = 25 MHz), voltage 3.3±0.3 V

#X2SPD pin = "0" (x2 speed mode): 17.5 MHz max. (CPU operating frequency = 20 MHz), voltage 3.3±0.3 V

BCU Configuration

The SDRAM interface control registers are allocated to addresses 0x39FFC0–0x39FFCA in area 6. Therefore,

before the control registers can be accessed, the BCU must be set up following the procedure described below.

1. CEFUNC[1:0] (D[A:9])/DRAM timing set-up register (0x48130) = "00" (default) or "01"

Set CEFUNC[1:0] = "00" to use SDRAM in areas 7/8 or CEFUNC[1:0] = "01" to use SDRAM in areas

13/14.

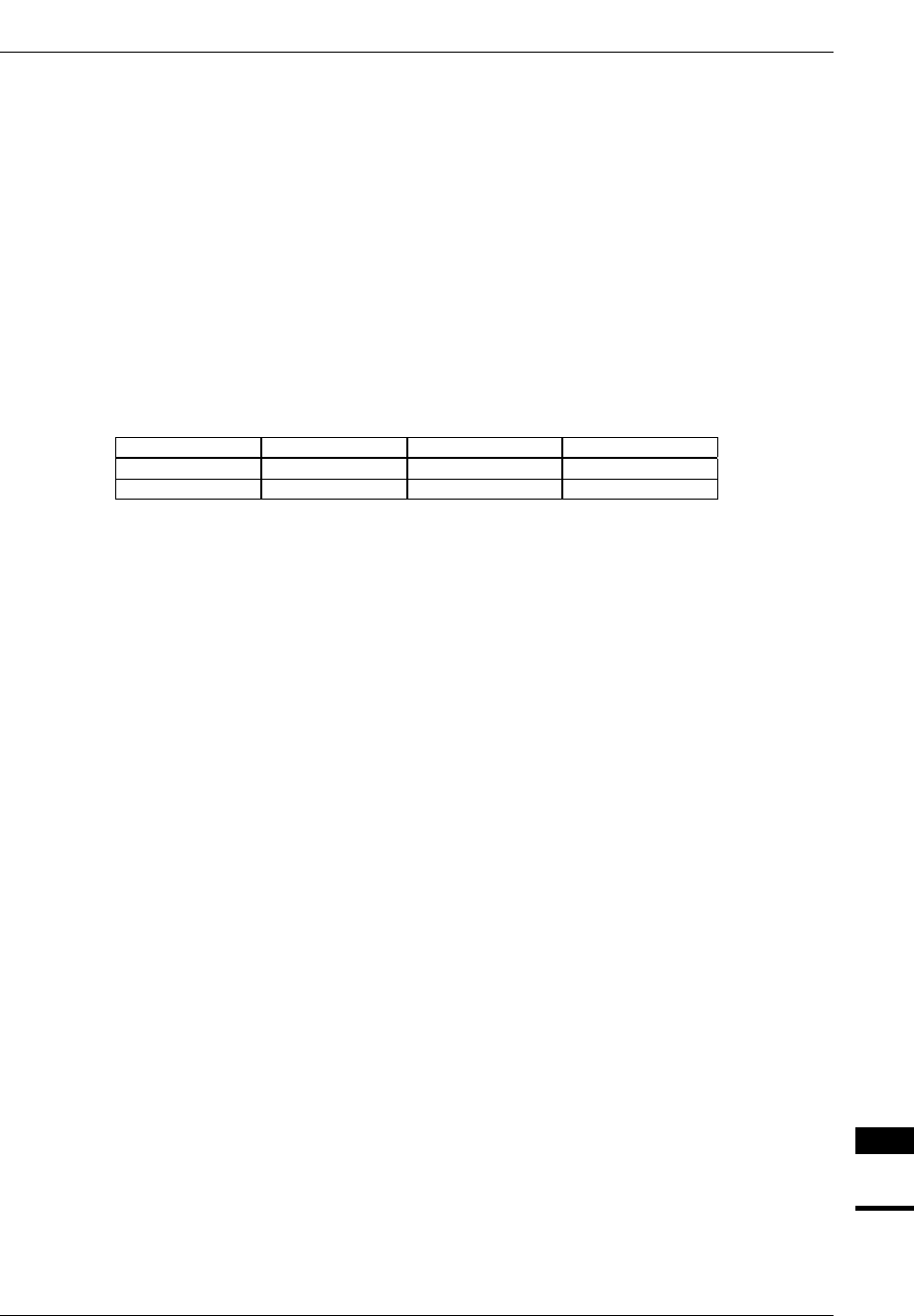

Table 2.3 Switching of #CE Output

PinCEFUNC = "00" CEFUNC = "01" CEFUNC = "1x"

#CE7/#SDCE0 #CE7/#SDCE0 #CE13/#SDCE0 #CE13/#SDCE0

#CE8/#SDCE1 #CE8/#SDCE1 #CE14/#SDCE1 #CE14/#SDCE1

(Default: CEFUNC = "00")

2. A6IO (D9)/Access control register (0x48132) = "1"

This ensures that the internal devices are accessed in area 6.

3. A6WT[2:0] (D[A:8])/Areas 6–4 set-up register (0x4812A) = "010"

This causes two wait cycles to be inserted when accessing area 6. With a different number of wait cycles, data

may not be written to the control registers normally.

4. SWAITE (D0)/Bus control register (0x4812E) = "1"

This enables the #WAIT signal. The IC’s internal #WAIT signal is used when powering up the SDRAM.

5. A6EC (D1)/Access control register (0x48132) = LCDCEC (D0)/LCDC system control register (0x39FFFD)

Use these registers to match endian types when reading out area 6 and SDRAMC/LCDC. Both bits select

little endian when "0" or big endian when "1".

When the above settings are finished, the SDRAM control registers in area 6 can be accessed.

Next, set areas 7/8 or areas 13/14 in which SDRAMs are connected.

A. When using areas 7/8 (CEFUNC = "00")

Note: The same settings as those shown above are omitted.

A-1. A8IO (DA)/Access control register (0x48132) = "1"

This sets areas 7/8 for internal access.

A-2. A8WT[2:0] (D[2:0])/Areas 8–7 set-up register (0x48128) = "000"

This sets areas 7/8 for no-wait access.

A-3. A8SZ (D6)/Areas 8–7 set-up register (0x48128) = SDRSZ (D6)/SDRAM advanced control register

(0x39FFC9)

Use these registers to ensure that the device size of areas 7/8 and that of the SDRAM controller are the same,

and are matched to the SDRAM data width. Both bits select 16 bits when "0" or 8 bits when "1".

A-4. A8DF[1:0] (D[5:4])/Areas 8–7 set-up register (0x48128)

If the system has an external memory device other than an SDRAM connected to it and accesses that memory

device and SDRAM in succession, set the output disable delay time of areas 7/8 to 2.5 cycles (A8DF[1:0] =

"10").

When only the SDRAM is read and no other external device is accessed, set the output disable delay time of

areas 7/8 to 0.5 cycles (A8DF[1:0] = "00") in order to reduce the SDRAM access time.