III PERIPHERAL BLOCK: INPUT/OUTPUT PORTS

B-III-9-16 EPSON S1C33L03 FUNCTION PART

Since K50 is masked from interrupt by SMPK00, no interrupt occurs at that point (2) above.

Next, because K53 becomes "0" at (3), an interrupt is generated due to the lack of a match between the data

of the input pin K5[4:1] that is enabled for interrupt and that of the input comparison register SCPK0[4:1].

Since only a change in states in which the input data and the content of the input comparison register SCPK

become unmatched after being matched constitutes an interrupt generation condition as described above, no

interrupt is generated when a change in states from one unmatched state to another, as in (4), occurs.

Consequently, if another interrupt is to be generated again following the occurrence of an interrupt, the state

of the input pin must be temporarily restored to the same content as that of the input comparison register

SCPK, or the input comparison register SCPK must be set again. Note that the input pins masked from

interrupt by the SMPK register do not affect interrupt generation conditions.

An interrupt is generated for FPK1 in the same way as described above.

Control Registers of the Interrupt Controller

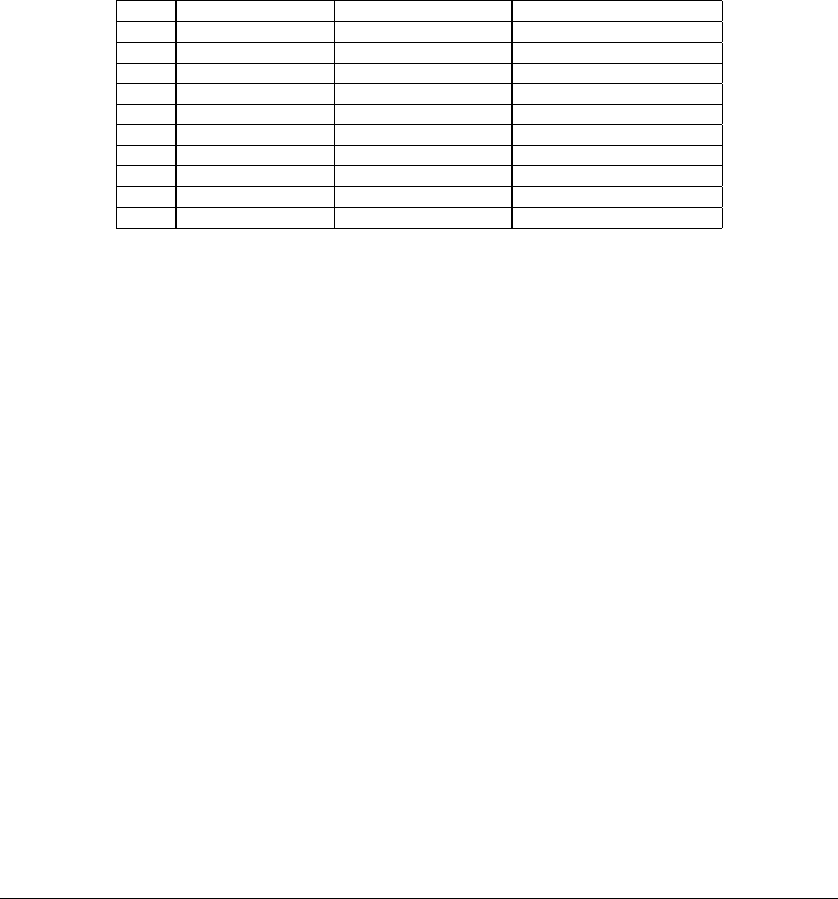

Table 9.8 shows the control registers of the interrupt controller that are provided for each input-interrupt

system.

Table 9.8 Control Registers of Interrupt Controller

System Interrupt factor flag Interrupt enable register Interrupt priority register

FPT7 FP7(D5/0x40287) EP7(D5/0x40277) PP7L[2:0](D[6:4]/0x4026D)

FPT6 FP6(D4/0x40287) EP6(D4/0x40277) PP6L[2:0](D[2:0]/0x4026D)

FPT5 FP5(D3/0x40287) EP5(D3/0x40277) PP5L[2:0](D[6:4]/0x4026C)

FPT4 FP4(D2/0x40287) EP4(D2/0x40277) PP4L[2:0](D[2:0]/0x4026C)

FPT3 FP3(D3/0x40280) EP3(D3/0x40270) PP3L[2:0](D[6:4]/0x40261)

FPT2 FP2(D2/0x40280) EP2(D2/0x40270) PP2L[2:0](D[2:0]/0x40261)

FPT1 FP1(D1/0x40280) EP1(D1/0x40270) PP1L[2:0](D[6:4]/0x40260)

FPT0 FP0(D0/0x40280) EP0(D0/0x40270) PP0L[2:0](D[2:0]/0x40260)

FPK1 FK1(D5/0x40280) EK1(D5/0x40270) PK1L[2:0](D[6:4]/0x40262)

FPK0 FK0(D4/0x40280) EK0(D4/0x40270) PK0L[2:0](D[2:0]/0x40262)

When the interrupt generation condition described above is met, the corresponding interrupt factor flag is set

to "1". If the interrupt enable register bit for that interrupt factor has been set to "1", an interrupt request is

generated.

Interrupts due to an interrupt factor can be disabled by leaving the interrupt enable register bit for that factor

set to "0". The interrupt factor flag is set to "1" whenever interrupt generation conditions are met, regardless

of the setting of the interrupt enable register.

The interrupt priority register sets the interrupt priority level (0 to 7) for each interrupt system. An interrupt

request to the CPU is accepted only when no other interrupt request of a higher priority has been generated.

In addition, only when the PSR's IE bit = "1" (interrupts enabled) and the set value of the IL is smaller than

the input interrupt level set using the interrupt priority register will the input interrupt request actually be

accepted by the CPU.

For details on these interrupt control registers, as well as the device operation when an interrupt has occurred,

refer to "ITC (Interrupt Controller)".

Intelligent DMA

The port input interrupt system can invoke an intelligent DMA (IDMA) through the use of its interrupt factor.

This enables the port inputs to be used as a trigger to perform DMA transfer.

The following shows the IDMA channel numbers assigned to each interrupt factor:

IDMA Ch. IDMA Ch.

FPT0 input interrupt: 1 FPT4 input interrupt: 28

FPT1 input interrupt: 2 FPT5 input interrupt: 29

FPT2 input interrupt: 3 FPT6 input interrupt: 30

FPT3 input interrupt: 4 FPT7 input interrupt: 31

For IDMA to be invoked, the IDMA request and IDMA enable bits shown in Table 9.9 must be set to "1" in

advance. Transfer conditions, etc. must also be set on the IDMA side in advance.