V DMA BLOCK: IDMA (Intelligent DMA)

B-V-3-12 EPSON S1C33L03 FUNCTION PART

Linking

If the IDMA channel number to be executed next is set in the IDMA link field "LNKCHN" of control information

and LNKEN is set to "1" (link enabled), DMA successive transfer in that IDMA channel can be performed.

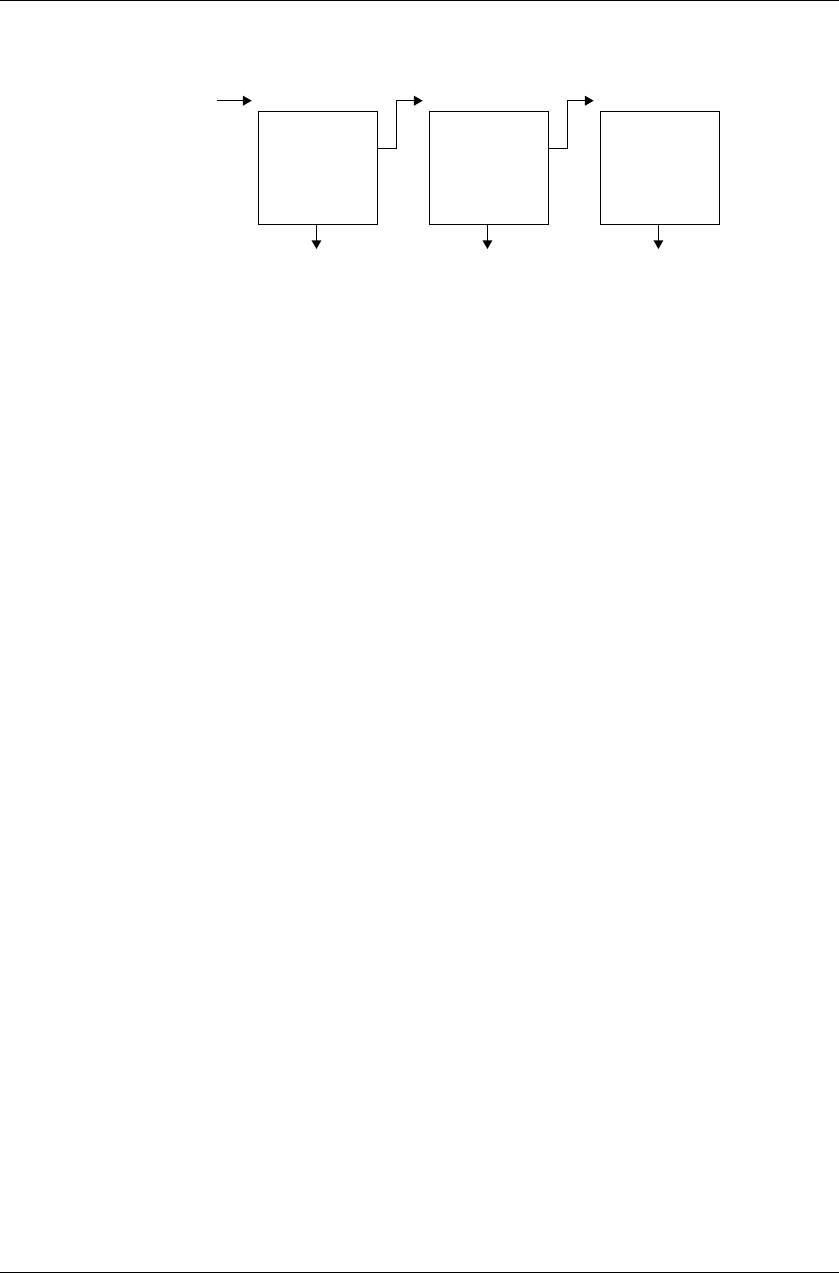

An example of link setting is shown in Figure 3.6.

Ch.3Trigger

After transfer TC = 0

LNKEN = 1

LNKCHN = 5

DMOD = 01

DINTEN = 1

TC = 1024

Ch.5

TC = 7

LNKEN = 1

LNKCHN = 7

DMOD = 00

DINTEN = 1

TC = 8

Ch.7

TC = 0

LNKEN = 0

LNKCHN = 9

DMOD = 10

DINTEN = 1

TC = 1

Figure 3.6 Example of Link Setting

For the above example, IDMA operates as described below.

•For trigger in hardware

(1) The IDMA channel 3 is invoked by an interrupt factor and the DMA transfer that is set is performed.

Since the IDMA is operating in successive transfer mode and the transfer counter is decremented to 0

and DINTEN is set to "1", the interrupt factor flag by which the channel 3 has been invoked remains set.

(2) Next, a DMA transfer is performed via the linked IDMA channel 5. Channel 5 is set for single transfer

mode and the transfer counter in this transfer is decremented by 1.

(3) Finally, a DMA transfer in IDMA channel 7 is performed. Although the channel 7 is set for block

transfer mode, the transfer counter is decremented to 0 when the transfer is completed because the

number of transfers to be performed is 1.

(4) Since the interrupt factor flag that has invoked IDMA channel 3 in (1) remains set, an interrupt is

generated when the IDMA transfer (channel 7) in (3) is completed. The transfer result does not affect the

interrupt factor flag of channel 3.

To generate an interrupt at the end of an IDMA transfer, the DINTEN (end-of-transfer interrupt enable)

bits in the IDMA control information for the first IDMA channel to be invoked and all the channels to be

linked must be set to "1".

• For trigger in the software application

(1) The IDMA channel 3 is invoked by a trigger in the software application and the DMA transfer that is set

is performed.

Since the IDMA is operating in successive transfer mode and the transfer counter is decremented to 0

and DINTEN is set to "1", the IDMA interrupt factor flag FIDMA (D4)/DMA interrupt factor flag

register (0x40281) is set when the transfer is completed.

(2) Next, a DMA transfer is performed in the linked IDMA channel 5. The channel 5 is set for the single

transfer mode and the transfer counter in this transfer is decremented by 1.

(3) Finally, a DMA transfer in IDMA channel 7 is performed. Although channel 7 is set for the block

transfer mode, the transfer counter is decremented to 0 when the transfer is completed because the

number of transfers to be performed is 1. The completion of this transfer also causes the FIDMA flag to

be set to "1". However, the FIDMA flag has already been set when the transfer is completed in (1) above.

(4) Since the FIDMA flag is set, an interrupt request is generated here. In cases when IDMA has been

invoked by a trigger in the software application, if the transfer counter in any one of the linked channels

is decremented to 0 and DINTEN for that channel is set to "1", an interrupt request for the completion of

IDMA transfer is generated when a transfer operation in each of the linked channels is completed. The

channel in which an interrupt request has been generated can be verified by reading out the transfer

counter.

Transfer operations in each channel are performed as described earlier.