III PERIPHERAL BLOCK: SERIAL INTERFACE

B-III-8-26 EPSON S1C33L03 FUNCTION PART

If an interrupt factor occurs when the IDMA request and enable bits are set to "1", IDMA is invoked. No

interrupt request is generated at that point. An interrupt request is generated upon completion of the DMA

transfer. The bits can also be set so as not to generate an interrupt, with only a DAM transfer performed.

For details on DMA transfer and how to control interrupts upon completion of DMA transfer, refer to "IDMA

(Intelligent DMA)".

•Ch.2 and Ch.3

For Ch.2 and Ch.3, either a port input interrupt or 16-bit timer interrupt is selected, and IDMA is initialed by

means of that interrupt factor.

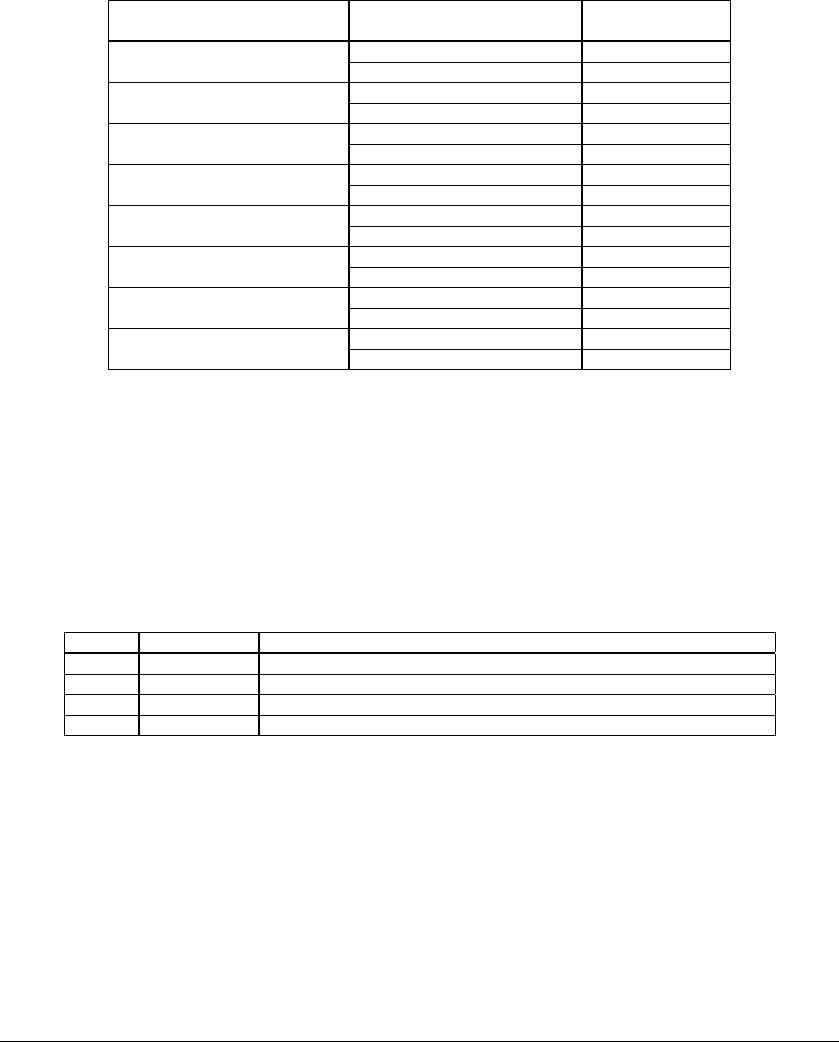

The correspondence between IDMA channels and Serial I/F Ch.2 and Ch.3 is shown in Table 8.12.

Table 8.12 Correspondence to IDMA Channels

Serial I/F Ch.2, Ch.3 /

T8-Ch.4, Ch.5 interrupt factor

Port input / 16-bit timer

interrupt factor

IDMA Ch.

T8 Ch.5 UF FPT7 31

Timer 2 compare A 12

T8 Ch.4 UF FPT5 29

Timer 2 compare B 11

SIO Ch.3 TXD Emp. FPT6 30

Timer 4 compare A 16

SIO Ch.3 RXD Full FPT4 28

Timer 4 compare B 15

SIO Ch.3 RXD Err. FPT2 3

Timer 3 compare A 14

SIO Ch.2 TXD Emp. FPT3 4

Timer 5 compare A 18

SIO Ch.2 RXD Full FPT1 2

Timer 5 compare B 17

SIO Ch.2 RXD Err. FPT0 1

Timer 3 compare B 13

For example, when port input interrupts are selected, Serial I/F Ch.2 transmit buffer empty corresponds to

port 3, and to IDMA Ch.4. Therefore, IDMA can be invoked by setting both IDMA request bit RP3

(D3/0x40290) and IDMA enable bit DEP3 (D3/0x40294) to "1".

High-speed DMA

•Ch.0 and Ch.1

The receive-buffer full interrupt and transmit-buffer empty interrupt factors can also invoke high-speed DMA

(HSDMA).

The following shows the HSDMA channel number and trigger set-up bit corresponding to each channel:

Table 8.13 HSDMA Trigger Set-up Bits

SIF Ch. HSDMA Ch. Trigger set-up bits

00HSD0S[3:0] (D[3:0]) / HSDMA Ch.0/1 trigger set-up register (0x40298)

11HSD1S[3:0] (D[7:4]) / HSDMA Ch.0/1 trigger set-up register (0x40298)

02HSD2S[3:0] (D[3:0]) / HSDMA Ch.2/3 trigger set-up register (0x40299)

13HSD3S[3:0] (D[7:4]) / HSDMA Ch.2/3 trigger set-up register (0x40299)

For HSDMA to be invoked by the receive-buffer full interrupt factor, the trigger set-up bits should be set to

"1010". For HSDMA to be invoked by the transmit-buffer empty interrupt factor, the trigger set-up bits

should be set to "1011". Transfer conditions, etc. must also be set on the HSDMA side.

The HSDMA channel is invoked through generation of the interrupt factor.

For details on HSDMA transfer, refer to "HSDMA (High-Speed DMA)".