III PERIPHERAL BLOCK: SERIAL INTERFACE

B-III-8-46 EPSON S1C33L03 FUNCTION PART

Programming Notes

(1) Before setting various serial-interface parameters, make sure the transmit and receive operations are disabled

(TXENx = RXENx = "0").

(2) When the serial interface is transmitting or receiving data, do not set TXENx or RXENx to "0", and do not

execute the slp instruction.

(3) In clock-synchronized transfers, the mode of communication is half-duplex, in which the clock line is shared

between the transmit and receive units. Therefore, RXENx and TXENx cannot be enabled simultaneously.

(4) After an initial reset, the interrupt factor flag becomes indeterminate. To prevent generation of an unwanted

interrupt or IDMA request, reset this flag in the program.

(5) If a receive error occurs, the receive-error interrupt and receive-buffer full interrupt factors occur

simultaneously. However, since the receive-error interrupt has priority over the receive-buffer full interrupt,

the receive-error interrupt is processed first. Therefore, it is necessary to reset the receive-buffer full interrupt

factor flag through the use of the receive-error interrupt processing routine.

(6) To prevent the regeneration of interrupts due to the same factor following the occurrence of an interrupt,

always be sure to reset the interrupt factor flag before setting the PSR again or executing the reti instruction.

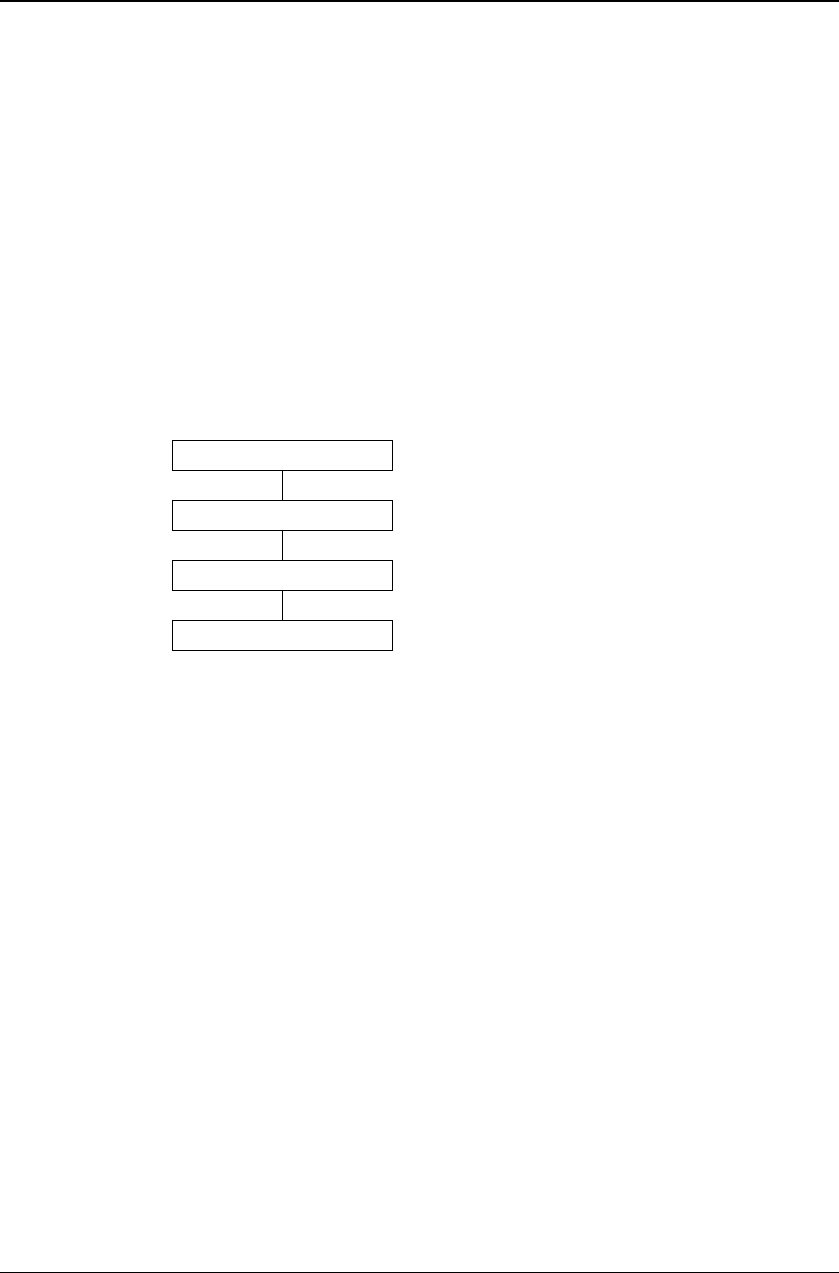

(7) Follow the procedure described below to initialize the serial interface.

Set IRMDx[1:0]

Set SMDx[1:0]

Other settings

Enable transmitting/receiving

"00"(normal I/F) or "10"(IrDA I/F)

Transfer mode setting

Data format and clock selection

Internal division ratio, IrDA I/O logic

and other settings

Enable transmitting, receiving or both

Figure 8.18 Serial Interface Initialize Procedure

(8) When transmitting data in the clock-synchronized master mode, transmit data is written to the transmit data

register after the initial setting is performed following the flow in item (7). However, the clock generated by

the 8-bit timer must be supplied to the serial interface (at least one underflow has had to have occurred in the

8-bit tier) before this writing. Otherwise, 0xFF will be transmitted prior to the written data.

(9) The maximum transfer rate of the serial interface is limited to 1 Mbps.

(10) If the receive circuit is stopped during reception, set both transmission and reception to the disabled status.

(11) When performing data transfer in the clock-synchronized mode, the division ratio of the prescaler and the

reload data for the 8-bit programmable timer should be set so that the baud-rate is 1/4 of the system clock

frequency or lower.

(12) The serial interface operates only when the prescaler is operating.