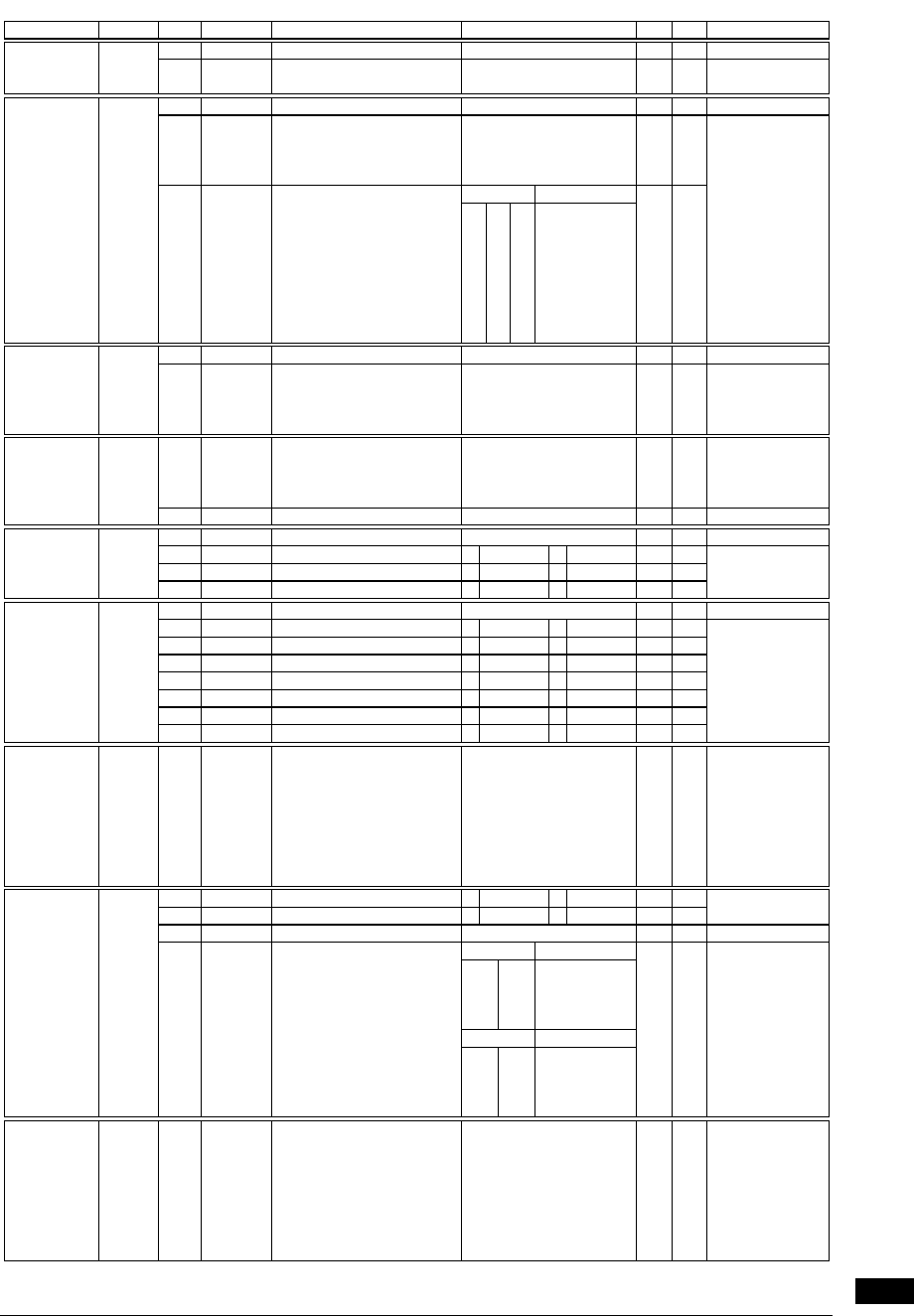

APPENDIX: I/O MAP

S1C33L03 FUNCTION PART EPSON B-APPENDIX-47

A-1

B-ap

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

S1VSIZE9

S1VSIZE8

D7–2

D1

D0

reserved

Screen 1 vertical size

(high-order 2 bits)

–

0

0

–

R/W

0 when being read.039FFF3

(B)

Screen 1

vertical size

register 1

–

–

FIFOEO3

FIFOEO2

FIFOEO1

FIFOEO0

LCLKSEL2

LCLKSEL1

LCLKSEL0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

FIFO empty offset

LCDC clock select

–

0

0

0

0

0

0

0

–

R/W

R/W

0 when being read.039FFF4

(B)

FIFO control

register

–

Fix at 8 (0b1000)

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

LCLKSEL[2:0]

LCDC clock

BCU_CLK/4

BCU_CLK/3

BCU_CLK/2

BCU_CLK

reserved

Stop

Stop

Stop

–

LUTADDR3

LUTADDR2

LUTADDR1

LUTADDR0

D7–4

D3

D2

D1

D0

reserved

Look-up table address

–

0

0

0

0

–

R/W

0 when being read.039FFF5

(B)

Look-up table

address

register

–

LUTDT3

LUTDT2

LUTDT1

LUTDT0

–

D7

D6

D5

D4

D3–0

Look-up table data

reserved

0

0

0

0

–

R/W

–

0 when being read.

039FFF7

(B)

Look-up table

data register

–

–

GPIO2C

GPIO1C

GPIO0C

D7–3

D2

D1

D0

reserved

GPIO2 configuration

GPIO1 configuration

GPIO0 configuration

–

0

0

0

–

R/W

R/W

R/W

0 when being read.039FFF8

(B)

GPIO

configuration

register

–

1 Output 0 Input

1 Output 0 Input

1 Output 0 Input

–

GPO6D

GPO5D

GPO4D

GPO3D

GPIO2D

GPIO1D

GPIO0D

D7

D6

D5

D4

D3

D2

D1

D0

reserved

GPO6 data

GPO5 data

GPO4 data

GPO3 data

GPIO2 data

GPIO1 data

GPIO0 data

–

0

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.039FFF9

(B)

GPIO

status/control

register

–

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

1 High 0 Low

SP1A7

SP1A6

SP1A5

SP1A4

SP1A3

SP1A2

SP1A1

SP1A0

D7

D6

D5

D4

D3

D2

D1

D0

Scratch pad 0

0

0

0

0

0

0

0

R/W039FFFA

(B)

Scratch pad

register

–

PMODEN

PMODSEL

–

PMODCLK1

PMODCLK0

D7

D6

D5–2

D1

D0

Portrait mode enable

Portrait mode select

reserved

Portrait mode clock select

(LCDC clock division ratio)

Division ratio 1: Default mode

Division ratio 2: Alternate mode

P: Pixel clock, M: Memory clock

0

0

–

0

0

R/W

R/W

–

R/W

0 when being read.

039FFFB

(B)

1 Portrait 0 Landscape

1 Alternate 0 Default

Portrait mode

register

1

1

0

0

1

0

1

0

PMODCLK[1:0]

Division ratio 1

P: 1/8, M: 1/8

P: 1/4, M: 1/4

P: 1/2, M: 1/2

P: 1/1, M: 1/1

1

1

0

0

1

0

1

0

PMODCLK[1:0]

Division ratio 2

P: 1/8, M: 1/4

P: 1/4, M: 1/2

P: 1/2, M: 1/1

P: 1/2, M: 1/1

PMODLBC7

PMODLBC6

PMODLBC5

PMODLBC4

PMODLBC3

PMODLBC2

PMODLBC1

PMODLBC0

D7

D6

D5

D4

D3

D2

D1

D0

Line byte count 0

0

0

0

0

0

0

0

R/W039FFFC

(B)

Line byte

count register

for portrait

mode