88

CHAPTER 4 DELAYED INTERRUPT GENERATION MODULE

4.4 Explanation of Operation of Delayed Interrupt Generation

Module

The delayed interrupt generation module has a function for generating or canceling an

interrupt request by software.

■ Explanation of Operation of Delayed Interrupt Generation Module

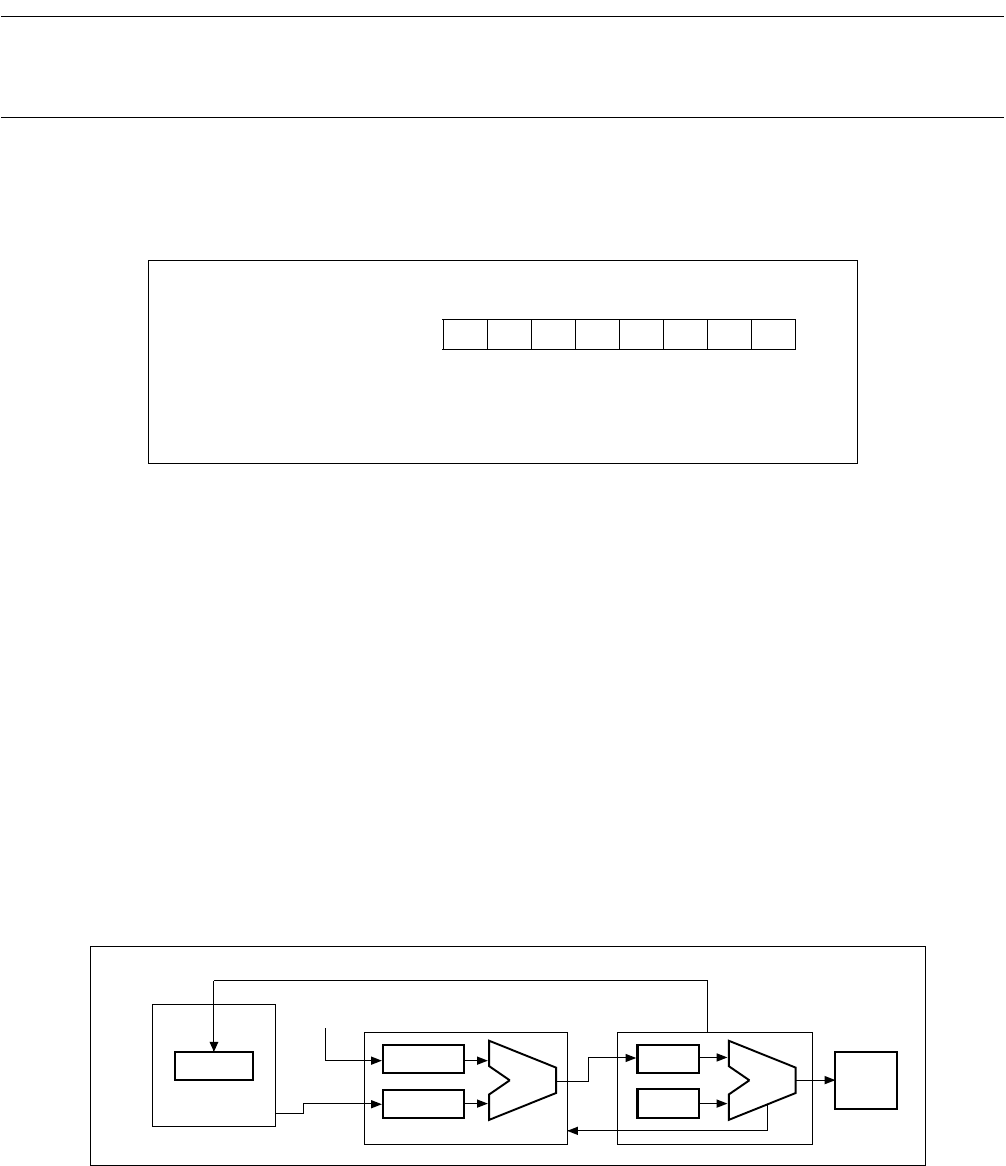

Using the delayed interrupt generation module requires the setting shown in Figure 4.4-1 .

Figure 4.4-1 Setting for Delayed Interrupt Generation Module

When the R0 bit in the delayed interrupt request generate/cancel register (DIRR) is set to "1" (DIRR: R0 =

1), an interrupt request is generated. There is no interrupt request enable bit.

●

Operation of delayed interrupt generation module

• When the R0 bit in the delayed interrupt request generate/cancel register (DIRR) is set to "1", the

interrupt request latch is set to "1" and an interrupt request is generated to the interrupt controller.

• An interrupt request is generated to the CPU when the interrupt controller prioritizes the interrupt

request over other requests.

• When the interrupt level mask bit of the condition code register (CCR: ILM) is compared to the

interrupt request level (ICR: IL), and the interrupt request level is higher than ILM, CPU executes the

delayed interrupt processing after the instruction currently being executed is completed.

• At interrupt processing, the user program sets the R0 bit to 0 to cancel the interrupt request and performs

task switching.

Figure 4.4-2 shows the operation of the delayed interrupt generation module.

Figure 4.4-2 Operation of Delayed Interrupt Generation Module

− : Undefined bit

❍

: Used bit

bit151413121110 9bit8

DIRR

−−−−−−−R0

❍

DIRR

ICR YY

ICR XX

CMP

IL

ILM

CMP

CPU

Delayed interrupt generation module

Other

request

Interrupt controller

Interrupt

processing