347

CHAPTER 18 8-/10-BIT A/D CONVERTER

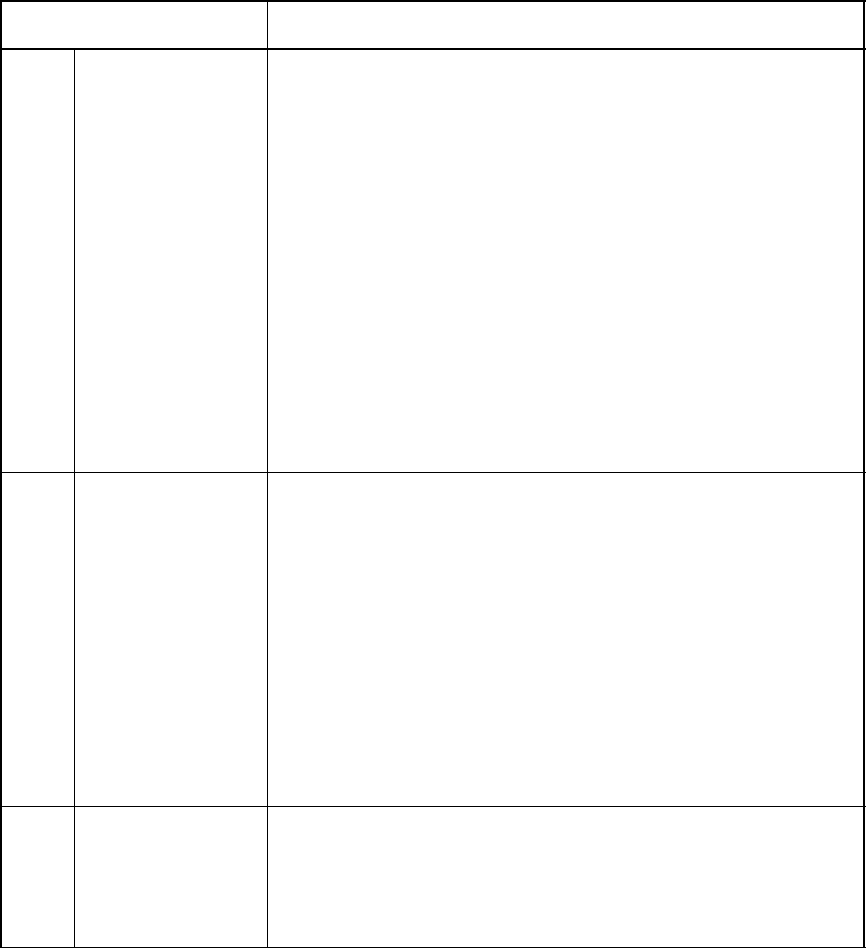

Table 18.3-2 Function of Each Bit of A/D Control Status Register (High) (ADCS1) (1/2)

Bit name Function

bit15 BUSY:

A/D conversion-on

flag bit

This bit forcibly terminates the 8-/10-bit A/D converter. When read, this

bit indicates whether the 8-/10-bit A/D converter is operating or

stopped.

When set to "0": Forcibly terminates 8-/10-bit A/D converter

When set to "1": No effect

Read: 1 is read when the 8-/10-bit A/D converter is operating and 0 is

read when the converter is stopped.

Note:

• "1" is read from this bit when an read-modify-write instruction is

used.

• In the single-shot mode, this bit is cleared when A/D conversion

ends.

• In the continuous or pause mode, the A/D conversion does not

stop until writing "0" to this bit.

• Do not perform the forced stop (BUSY=0) and the activation of

the A/D converter concurrently (using software (STRT=1), exter-

nal trigger, or timer).

bit14 INT:

Interrupt request flag

bit

This bit indicates that an interrupt request is generated.

• When A/D conversion is terminated and its results are stored in the

A/D data register (ADCR0, 1), the INT bit is set to "1".

• When the interrupt request flag bit is set (INT = 1) with an interrupt

request enabled (INTE = 1), an interrupt request is generated.

When set to "0": Cleared

When set to "1": No effect

When EI

2

OS function started: Cleared

Note:

• "1" is read from this bit when an read-modify-write instruction is

used.

• To clear the INT bit, write 0 when the 8-/10-bit A/D converter is

stopped.

bit13 INTE:

Interrupt request

enable bit

This bit enables or disables output of an interrupt request.

• When the interrupt request flag bit is set (INT =1) with an interrupt

request enabled (INTE = 1), an interrupt request is generated.

Note:

Always set this bit to 1 when the EI

2

OS function is used.