114

CHAPTER 6 CLOCK SUPERVISOR

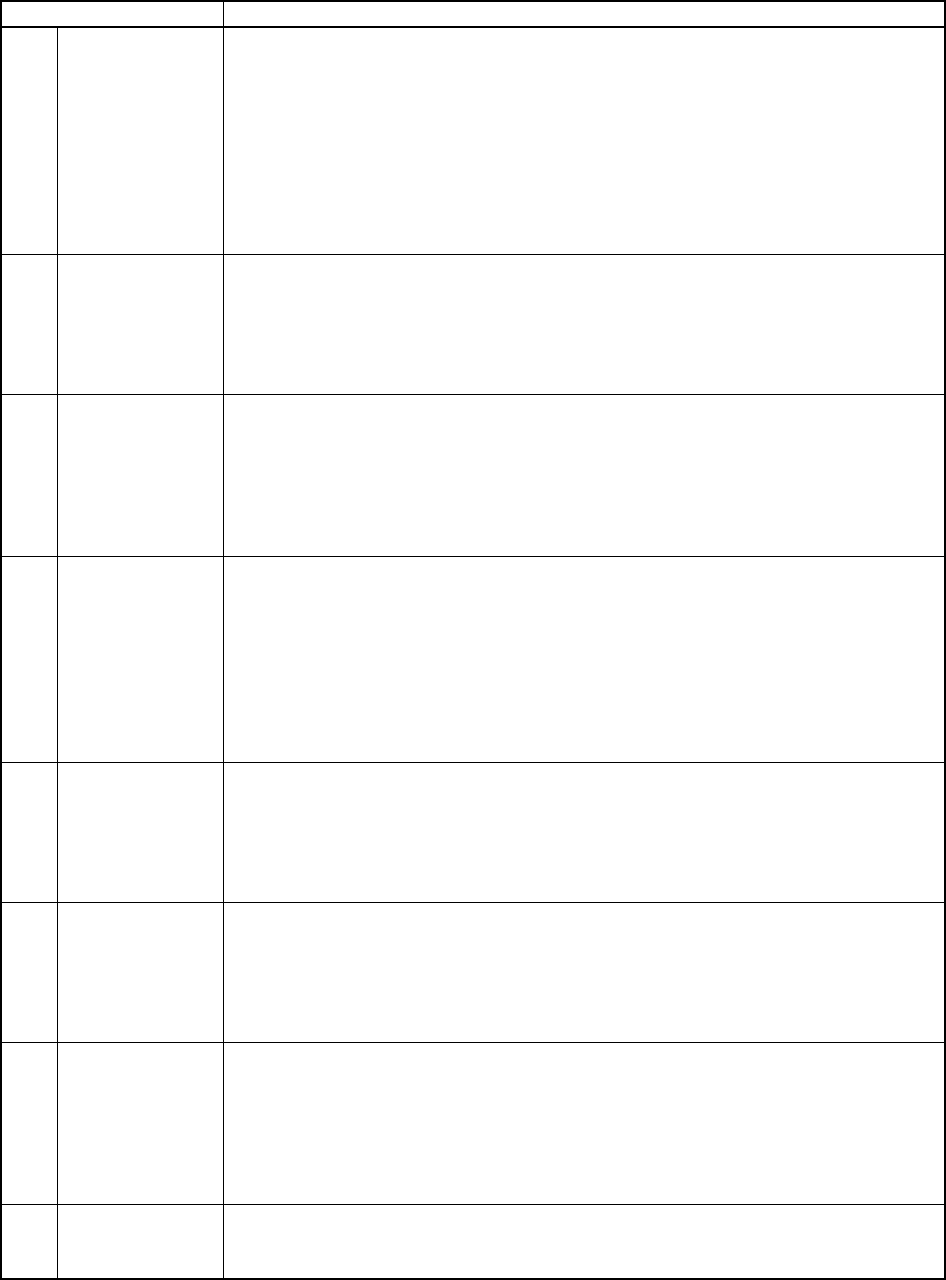

Bit name Function

bit7 SCKS

Sub clock select

This bit permits built-in CR oscillation clock to be used as a sub-clock. Only "S" suffix

product is valid to this function.

"1": It is possible to change to the sub clock mode with built-in CR oscillation clock.

"0": It is not possible to change to the sub clock mode.

This bit is initialized to "0" by power-on reset, external reset, or low voltage detection

reset in "T" suffix product. It is initialized to "0" by power-on reset or external reset

without "T" suffix product.

It is necessary to set this bit to "1" in the main clock mode before the sub-clock

supervisor after the above-mentioned is initialized operates automatically.

Moreover, after setting to "1", this bit cannot be reset to "0" by software.

bit6 MM

Main clock

missing

This bit indicates the oscillation missing of main clock terminal X0 and X1 was detected.

"1": Missing main clock has been detected.

"0": Missing main clock has not been detected.

This bit is initialized to "0" by power-on reset, external reset, or low voltage detection

reset with "T" suffix product.

It is initialized to "0" by power-on reset or external reset without "T" suffix product.

bit5 SM

Sub clock

missing

This bit indicates the oscillation missing of sub clock terminal X0A and X1A was

detected. No "S" suffix product is valid to this function.

"1": Missing sub-clock has been detected.

"0": Missing sub-clock has not been detected.

This bit is initialized to "0" by power-on reset, external reset, or low voltage detection

reset with "T" suffix product.

It is initialized to "0" by power-on reset or external reset without "T" suffix product.

bit4 RCE

CR oscillation

clock enable

This bit permits built-in CR oscillation.

"1": Built-in CR oscillation is enabled.

"0": Built-in CR oscillation is disabled.

This bit is initialized to "1" by power-on reset, external reset, or low voltage detection

reset with "T" suffix product.

It is initialized to "1" by power-on reset or external reset without "T" suffix product.

Please set this bit in "1" after confirming both the following:

- The supervisor of main and sub-clock is disabled.

- MM and SM bits are "0".

bit3 MSVE

Main clock

supervisor

enable

This bit permits monitoring for main clock oscillation.

"1": Main clock supervisor is enabled.

"0": Main clock supervisor is disabled.

This bit is initialized to "1" by power-on reset or low voltage detection reset with "T"

suffix product.

It is initialized to "1" by power-on reset or external reset without "T" suffix product.

bit2 SSVE

Sub clock

supervisor

enable

This bit permits monitoring for sub clock oscillation.

"1": Sub clock supervisor is enabled.

"0": Sub clock supervisor is disabled.

This bit is initialized to "1" by power-on reset or low voltage detection reset with "T"

suffix product.

It is initialized to "1" by power-on reset or external reset without "T" suffix product.

bit1 SRST

Sub-clock mode

reset

This bit permits the reset output when transmitting from main clock/PLL clock mode to

the sub-mode with sub-clock breakdown.

"1": Output reset.

"0": Not output reset

This bit is initialized to "0" by power-on reset, external reset, or low voltage detection

reset with "T" suffix product.

It is initialized to "0" by power-on reset or external reset without "T" suffix product.

bit0 Reserved bit This bit is reserved.

Be sure to write "0" to this bit.

Read value is always "0".