320

CHAPTER 17 DTP/EXTERNAL INTERRUPTS

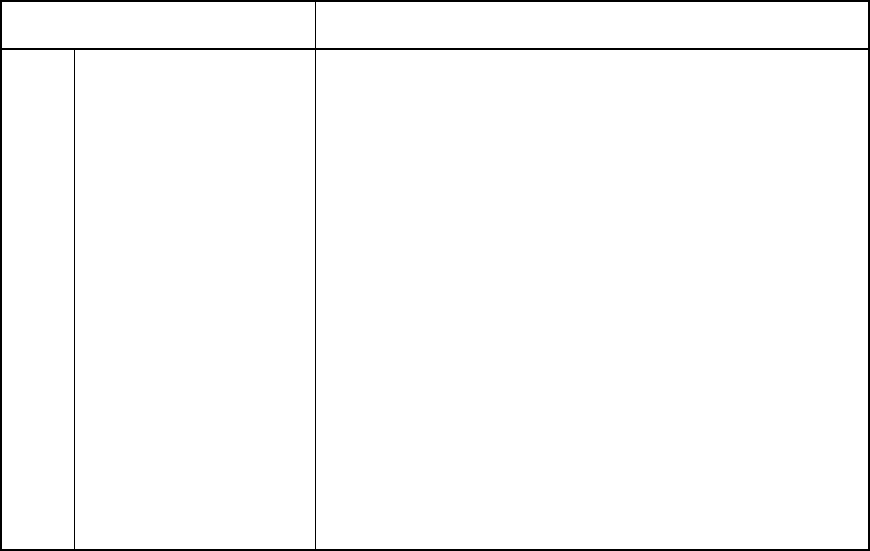

Table 17.3-2 Function of DTP/External Interrupt Factor Register (EIRR1)

Bit Name Function

bit8

to

bit15

ER15 to ER8(EIRR1),

DTP/External interrupt

request flag bits

These bits are set to "1" when the edges or level signals set by the

detection condition select bits in the detection level setting register

(ELVR1:LB, LA) are inputted to the DTP/external interrupt pins.

When set to "1": When the DTP/external interrupt request

enable bit (ENIR1:EN) is set to "1", an

interrupt request is generated to the

corresponding DTP/external interrupt channel.

When set to "0": Cleared

When set to "1": No effect

Note:

Reading by read-modify-write type instructions always returns

"1".

If more than one DTP/external interrupt request is enabled

(ENIR1:EN = 1), clear only the bit in the channel that accepts

an interrupt (EIRR1:ER = 0). No other bits must be cleared

unconditionally.

Reference:

When the EI

2

OS is started, the interrupt request flag bit is

automatically cleared after the completion of data transfer

(EIRR1:ER = 0).