538

CHAPTER 24 512K-BIT FLASH MEMORY

24.5 Starting the Flash Memory Automatic Algorithm

Three types of commands are available for starting the flash memory automatic

algorithm: Read/Reset, Write, and Chip Erase.

■ Command Sequence Table

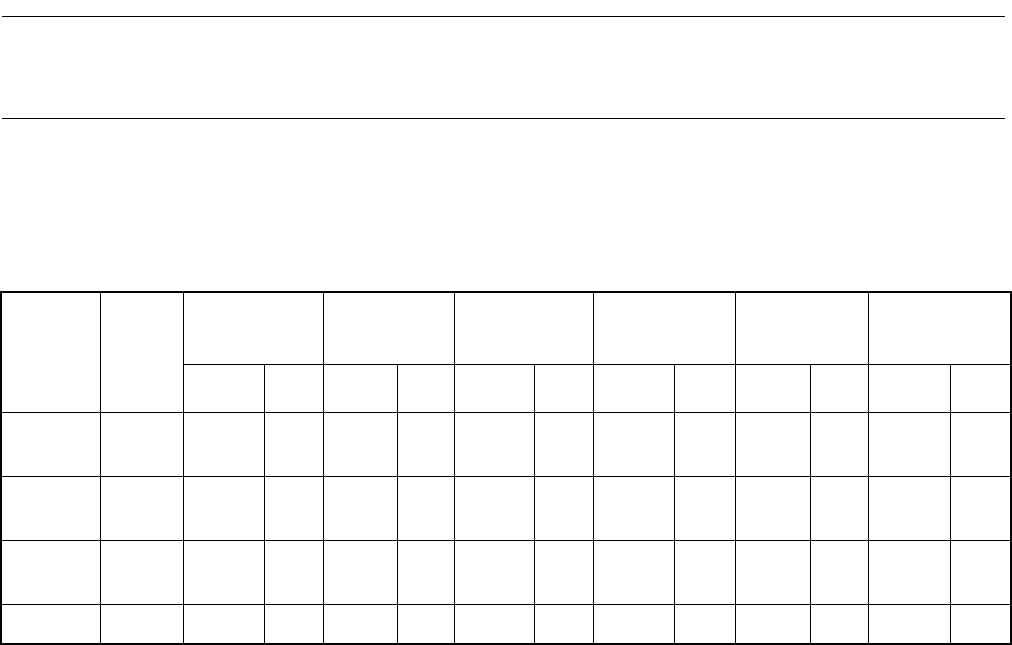

Table 24.5-1 lists the commands used for flash memory write/erase. All of the data written to the command

register is in bytes, but use word access to write. The data of the high-order bytes at this time is ignored.

Table 24.5-1 Command Sequence Table

Command

sequence

Bus

write

access

1st bus write

cycle

2nd bus write

cycle

3rd bus write

cycle

4th bus write

cycle

5th bus write

cycle

6th bus write

cycle

Address

Data

Address

Data

Address

Data

Address

Data

Address

Data

Address

Data

Read/

reset*

1

FFXXXX XXF0 - - - - - - - - - -

Read/

reset*

4

FFAAAA XXAA FF5554 XX55 FFAAAA XXF0 RA RD - - - -

Write

program

4

FFAAAA XXAA FF5554 XX55 FFAAAA XXA0 PA

(even)

PD

(word)

--- -

Chip erase 6

FFAAAA XXAA FF5554 XX55 FFAAAA XX80 FFAAAA XXAA FF5554 XX55 FFAAAA XX10

Notes:• Addresses in the table are the values in the CPU memory map. All addresses and data are hexadecimal values, where

"x" is any value.

• RA: Read address

• PA: Program address. Only even addresses can be specified.

• RD: Read data

• PD: Program data. Only word data can be specified.

*: Two kinds of read/reset commands can reset flash memory to the read mode.