51

CHAPTER 2 CPU

2.10 Interrupt Disable Instructions

Interrupt requests are not sampled for the following ten instructions:

- MOV ILM,#imm8 - PCB - SPB - OR CCR,#imm8 - NCC

- AND CCR,#imm8 - ADB - CMR - POPW PS - DTB

■ Interrupt Disable Instructions

If a valid hardware interrupt request occurs during execution of any of the above instructions, the interrupt

can be processed only when an instruction other than the above is executed. For details, see Figure 2.10-1 .

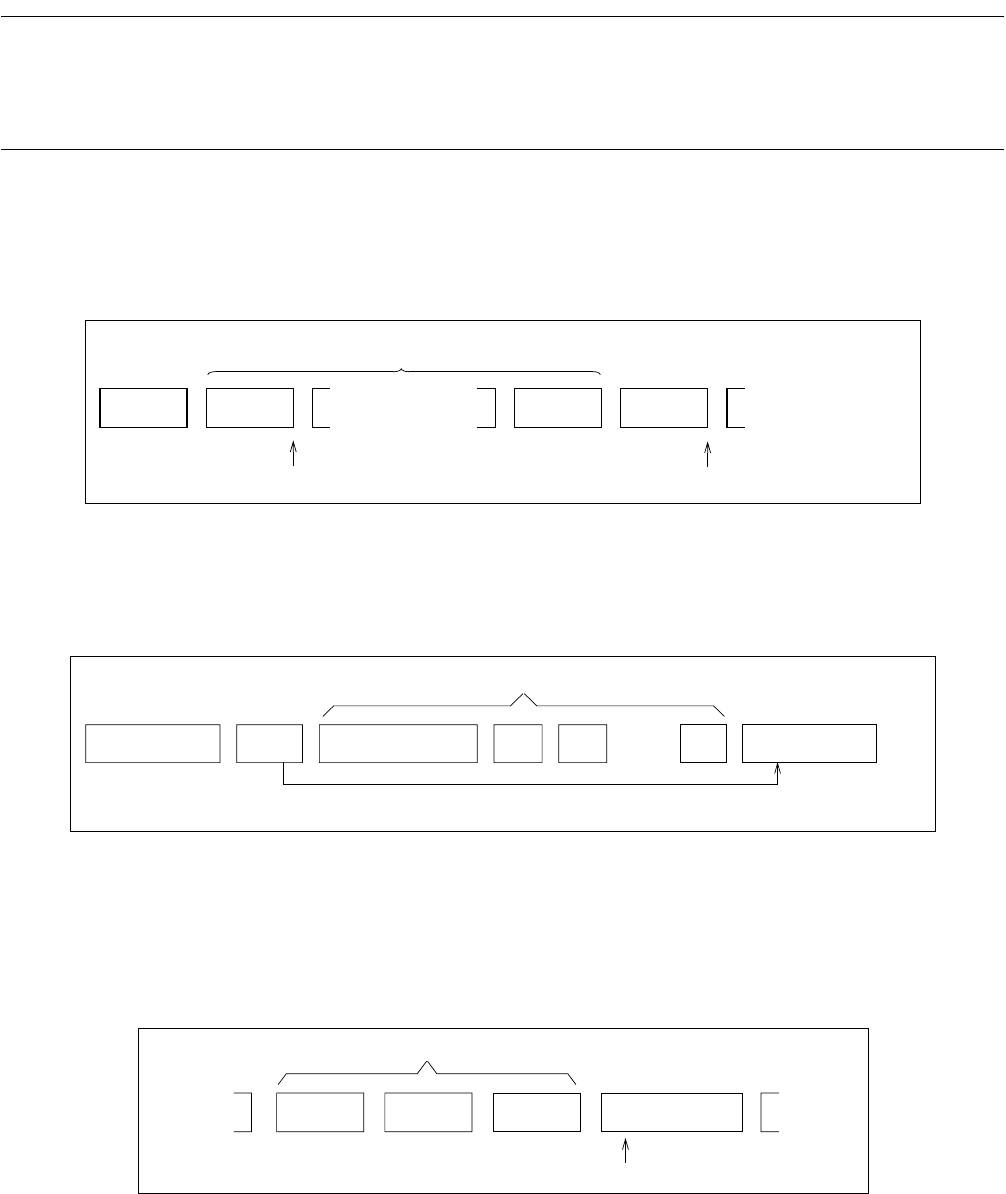

Figure 2.10-1 Interrupt Disable Instruction

■ Restrictions on Interrupt Disable Instructions and Prefix Instructions

When a prefix code is placed before an interrupt disable instruction, the prefix code affects the first

instruction after the code other than the interrupt disable instruction. For details, see Figure 2.10-2 .

Figure 2.10-2 Interrupt Disable Instructions and Prefix Codes

■ Consecutive prefix codes

When competitive prefix codes are placed consecutively, the latter becomes valid.

In the figure below, competitive prefix codes are PCB, ADB, DTB, and SPB.

For details, see Figure 2.10-3 .

Figure 2.10-3 Consecutive Prefix Codes

• • • • • • • •

(a)

(a)

• • •

Interrupt disable instruction

Ordinary

instruction

Interrupt request

Interrupt acceptance

• • • •

MOV A, FFH

CCR:XXX10XX

NCC ADD A,01

H

CCR:XXX10XX

MOV ILM,#imm8

Interrupt disable instruction

CCR does not change with NCC.

• • • • •• • • • •

ADB DTB PCB ADD A,01H

Prefix code

PCB is valid as the prefix

code.