393

CHAPTER 20 LIN-UART

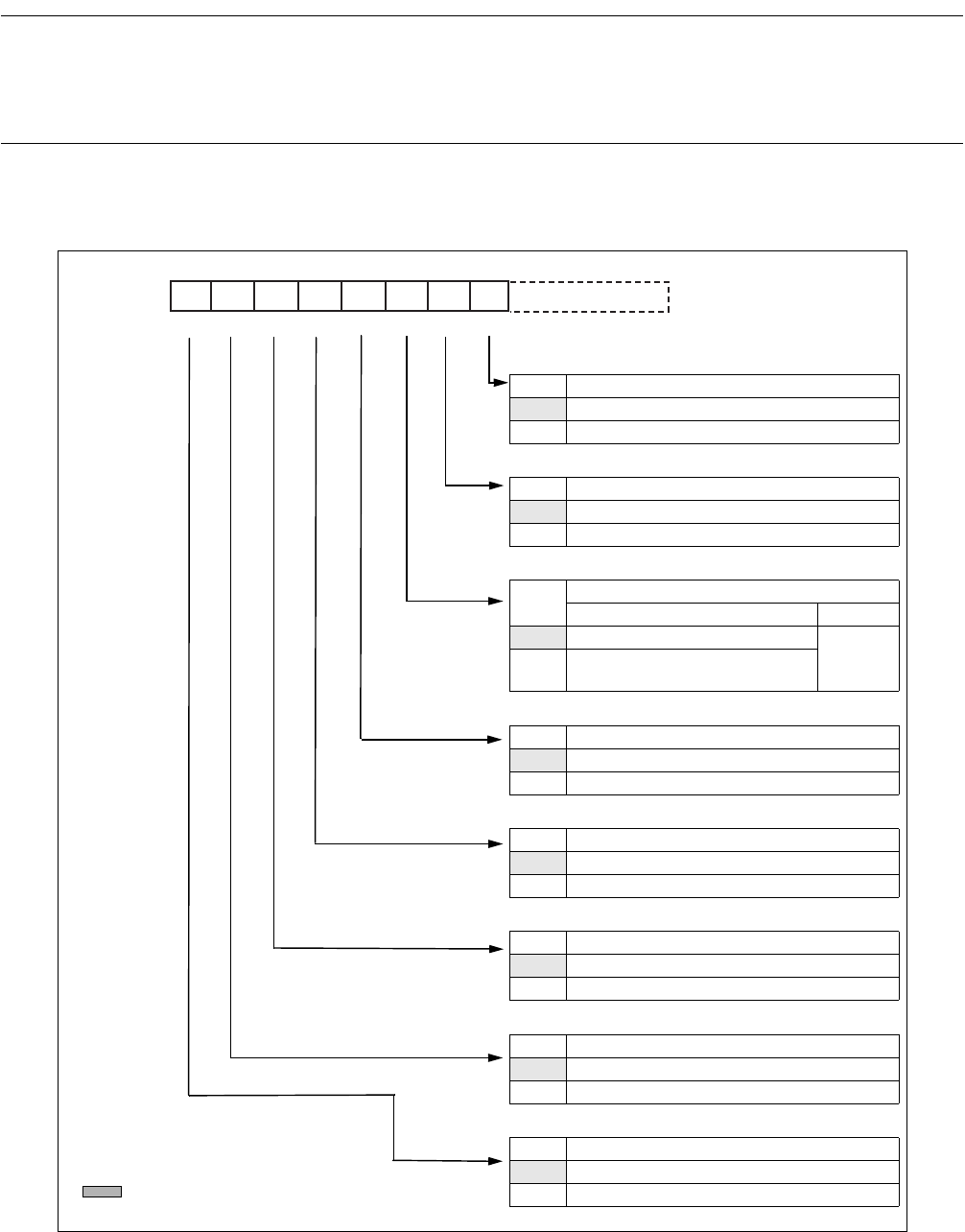

20.4.1 Serial Control Register (SCR)

This register specifies parity bits, selects the stop bit and data lengths, selects a frame

data format in mode 1, clears the reception error flag, and specifies whether to enable

transmission and reception.

■ Serial Control Register (SCR)

Figure 20.4-2 Configuration of the Serial Control Register (SCR)

PEN

P

SBL

CL

AD

CRE

RXE TXE

bit15

R/W

00000000

B

SCR0 : 000021

H

SCR1 : 000029

H

bit14

bit13

bit12

bit11 bit8

bit9

bit10

bit7 bit0

R/W

R/WR/W

R/W

R/W

W

R/W

bit8

TXE Transmission operation enable bit

0 Disable transmission

1 Enable transmission

bit9

RXE Reception operation enable bit

0 Disable reception

1 Enable reception

bit10

CRE

Clear reception error flag bit

Write Read

0 No effect

Read

always

returns 0

1

Clear all reception error flags

(PE, FRE, ORE)

bit11

AD Address/data format select bit

0 Data frame

1 Address frame

bit12

CL Data length select bit

07 bits

18 bits

bit13

SBL Stop bit length select bit

01 bit

12 bits

bit14

P Parity select bit

0 Even parity enabled

1 Odd parity enabled

bit15

PEN Parity enabled bit

0 Parity disabled

1 Parity enabled

R/W : Read/Write

W : Write only

: Initial value

Initial value

Address