155

CHAPTER 8 LOW-POWER CONSUMPTION MODE

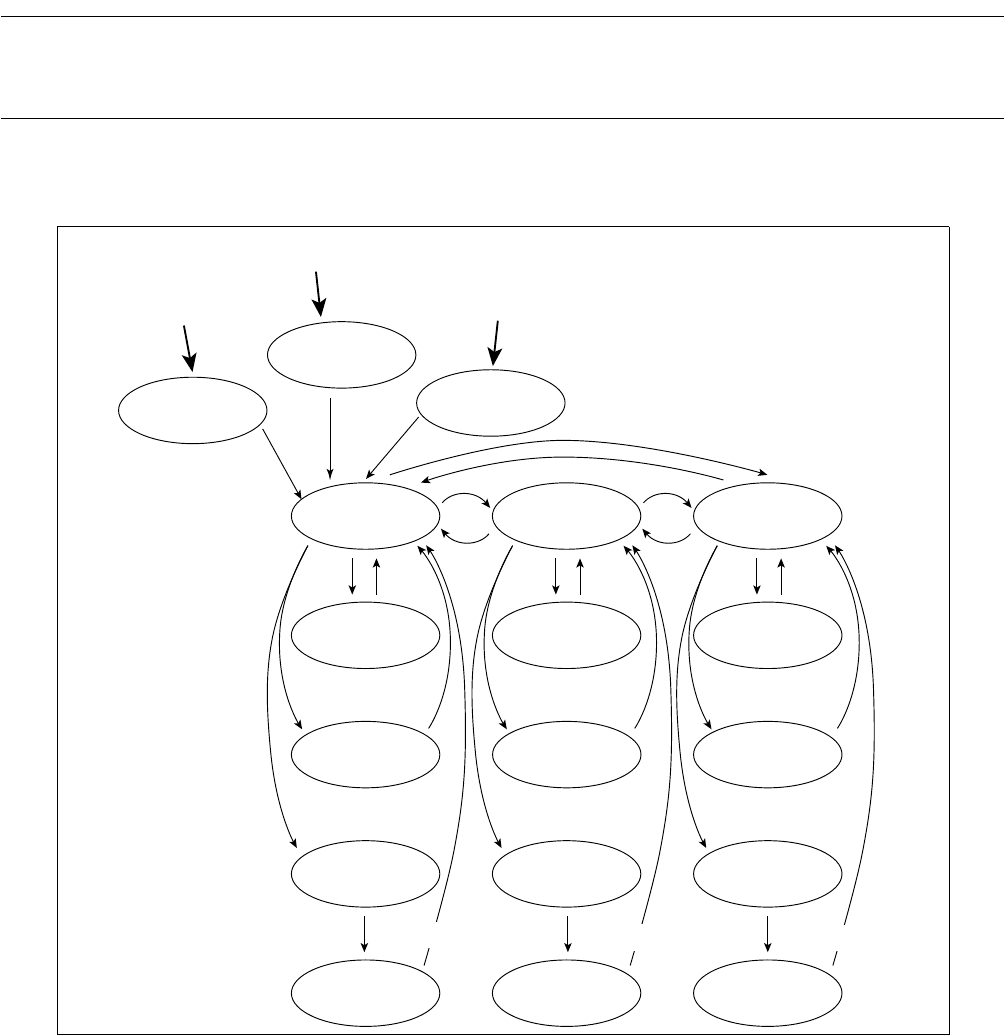

8.6 Status Change Diagram

Figure 8.6-1 shows the operation status and status transition in the clock mode and

standby mode of the MB90360 series.

■ Status Change Diagram

Figure 8.6-1 Status Change Diagram

Power-on

Power-on reset

Terminate of oscillation

stabilization wait

SLP=1

Interrupt

Interrupt

External reset, Watchdog timer reset, Software reset,

Clock supervisor reset, CPU operation detection reset

Reset

Main clock mode PLL clock mode

SCS=1

MCS=0

MCS=1

SCS=0

Subclock mode

Subsleep mode

Watch mode

Substop mode

Subclock

oscillation stabilization

wait

PLL sleep mode

PLL stop mode

Main clock

oscillation stabilization

wait

Main sleep mode

Main timebase timer

mode

PLL timebase timer

mode

Main stop mode

Main clock

oscillation stabilization

wait

Interrupt Interrupt

SLP=1

Interrupt

SLP=1

Interrupt

TMD=0

Interrupt

TMD=0

Interrupt

TMD=0

STP=1 STP=1 STP =1

Interrupt

SCS=0

SCS=1

Terminate of oscillation

stabilization wait

Terminate of oscillation

stabilization wait

Terminate of oscillation

stabilization wait

Drop power supply voltage

(4.0 V)

Low voltage

detection reset