346

CHAPTER 18 8-/10-BIT A/D CONVERTER

18.3.1 A/D Control Status Register (High) (ADCS1)

The A/D control status register (High) (ADCS1) provides the following settings:

• Starting A/D conversion function by software

• Selecting start trigger for A/D conversion

• Storing A/D conversion results in A/D data register to enable or disable interrupt

request

• Storing A/D conversion results in A/D data register to check and clear interrupt

request flag

• Pausing A/D conversion and checking state during conversion

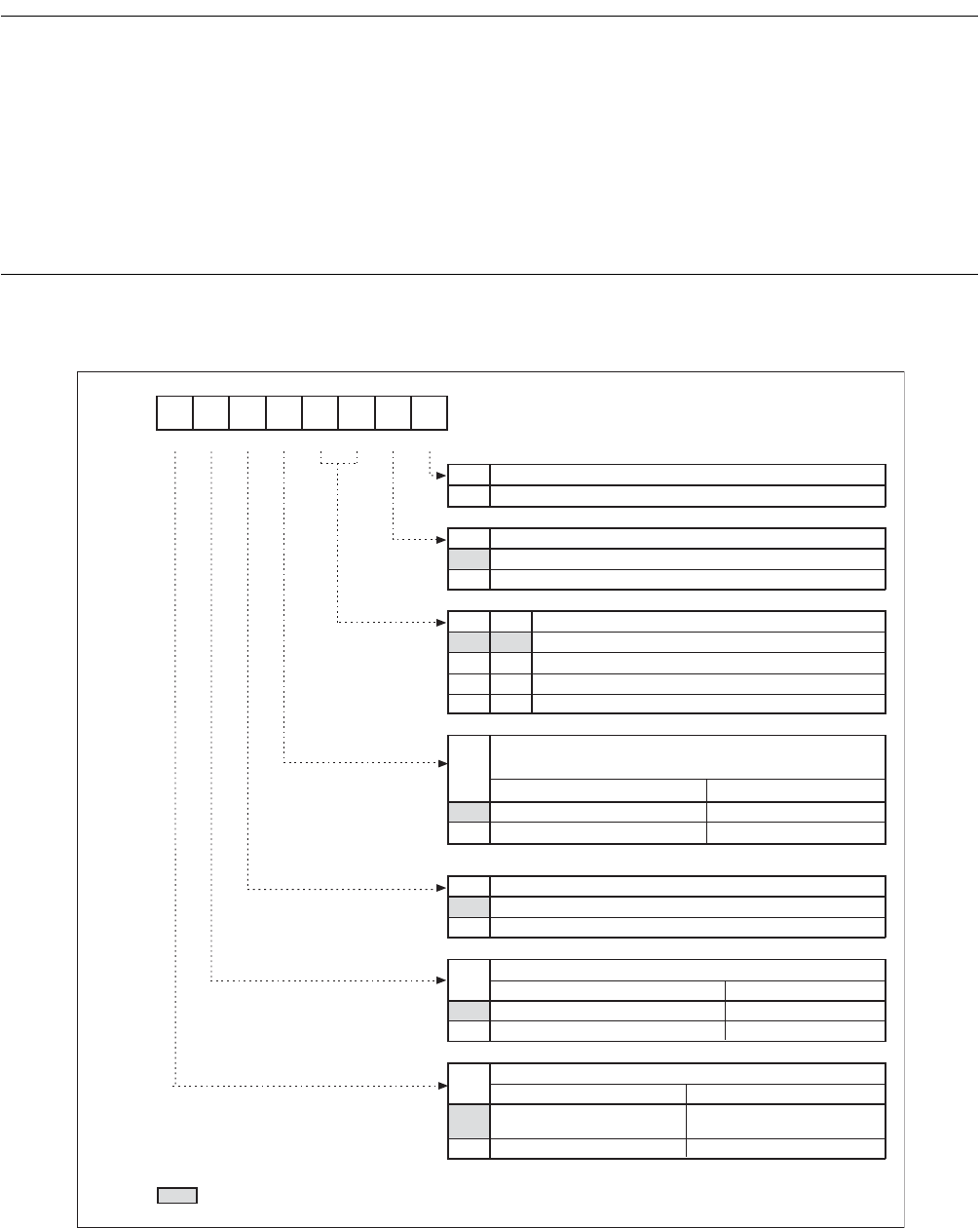

■ A/D Control Status Register (High) (ADCS1)

Figure 18.3-2 A/D Control Status Register (High) (ADCS1)

Reset value

0000000X

B

1213 11 10 9 8

bit8

14

15

STRT

0

1

Not starting A/D conversion function

Starting A/D conversion function

A/D conversion software starting bit

bit9

Read value is always 1.

Undefined bit

STS1

0

0

1

1

Starting software

Starting software or external trigger

Starting software

Starting software or external trigger

A/D conversion starting trigger select bit

bit11

0

1

PAUS

Suspended flag bit

(This bit is enabled only when EI

2

OS is used.)

bit12

INTE

0

1

Interrupt request disable

Interrupt request enable

Interrupt request enable bit

bit13

WR/WR/WR/WR/WR/W

R/W

STS0

0

1

0

1

bit10

0

1

INT

A/D conversion not terminated

A/D conversion terminated

Clear to "0"

No effect

Interrupt request flag bit

Read Write

Read Write

bit14

0

1

BUSY

A/D conversion terminated

(inactive state)

A/D conversion in operation

Terminates A/D conversion

forcibly

No effect

A/D conversion-on flag bit

bit15

BUSY

INT

INTE

PAUS STS1 STS0 STRT

−

−

-

Address

000069

H

Read Write

Conversion is not suspended.

Conversion is suspended.

Clear to "0".

No effect.

X

W

−

R/W : Read/Write

: Write only

: Reset value

: Undefined bit

: Indeterminate