456

CHAPTER 21 CAN CONTROLLER

21.4.3 Correspondence between Node Status Bit and Node

Status

Node status bit shows the node status by two bits (NS1 and NS0).

■ Correspondence between Node Status Bit and Node Status

Note:

Warning (error active) is included in the error active in CAN Specification 2.0B for the node status,

however, indicates that the transmit error counter or receive error counter has exceeded 96. The node

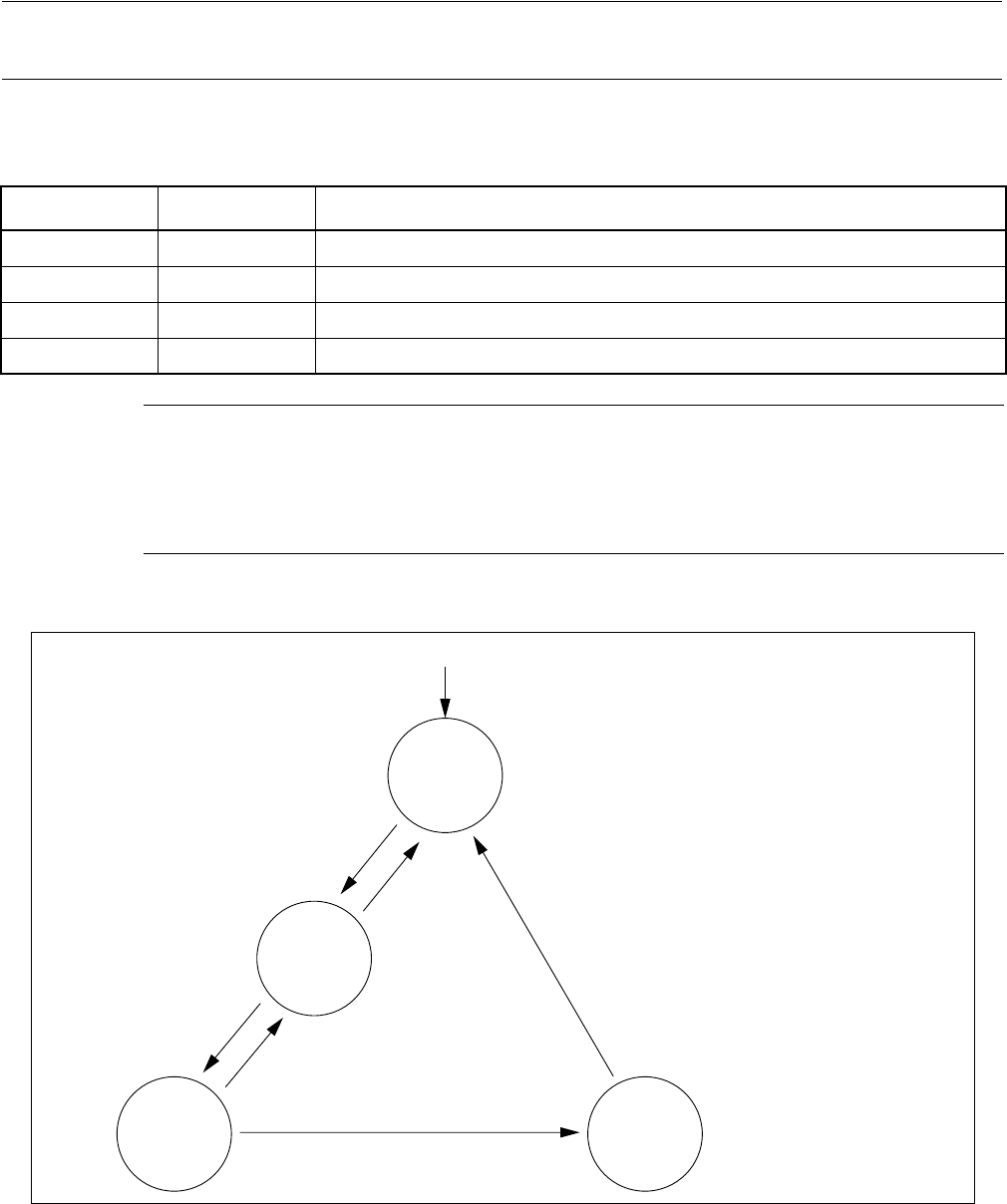

status change diagram is shown in Figure 21.4-3 .

Figure 21.4-3 Node Status Transition Diagram

Table 21.4-3 Correspondence between NS1 and NS0 and Node Status

NS1 NS0 Node status

00Error active

0 1 Warning (error active)

1 0 Error passive

1 1 Bus off

Error active

Hardware reset

Error passive

TEC ≥ 256

REC < 96

and TEC < 96

After 0 has been written to the HALT bit of

the register (CSR), continuous 11-bit High

levels (recessive bits) are input 128 times

to the the shift.

It is necessary to cancel the bus operation halt for the shift.

REC: Receive error counter

TEC: Transmit error counter

REC < 128

and TEC < 128

REC ≥ 96

or TEC ≥ 96

REC ≥ 128

or TEC ≥ 128

Bus off

(HALT=1)

Warning

(Error active)