247

CHAPTER 14 16-BIT RELOAD TIMER

14.3.2 Timer Control Status Registers (Low) (TMCSR: L)

The timer control status registers (Low) (TMCSR:L) enables or disable the timer

operation, check the generation of a software trigger or an underflow, enables or

disable an underflow interrupt, select the reload mode, and set the output of the TOT

pin.

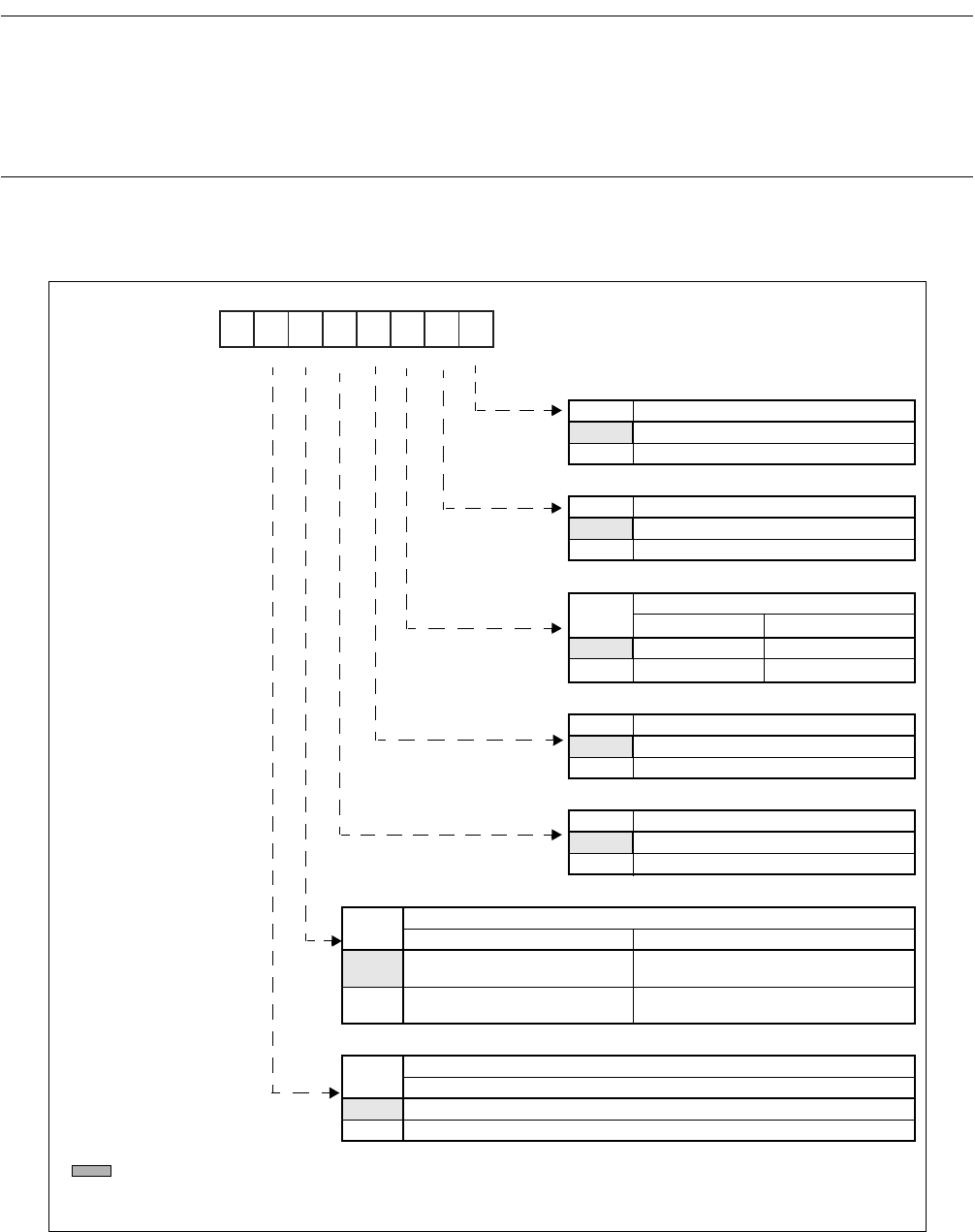

■ Timer Control Status Registers (Low) (TMCSR: L)

Figure 14.3-4 Timer Control Status Registers (Low) (TMCSR: L)

∗

00000000

B

45321

6

R/W R/W R/W R/W R/W R/W R/W

0

7

TMCSR2 : 000064

H

TMCSR3 : 000066

H

TRGCNTEUFINTERELDOUTLOUTE

R/W : Read/Write

: Reset value

∗ : For MOD0 (bit 7), see "14.3.1 Timer Control Status Registers (High) (TMCSR:H)".

Reset value

Address:

bit0

TRG Software trigger bit

0No effect

1 After reloading, starts counting

bit1

CNTE Timer operation enable bit

0 Timer operation disabled

1 Timer operation enabled (wait start trigger)

bit2

UF

Underflow generating flag bit

Read Write

0 No underflow Clear UF bit

1 Underflow No effect

bit3

INTE Underflow interrupt enable bit

0 Underflow interrupt disable

1 Underflow interrupt enable

bit4

RELD Reload select bit

0 One-shot mode

1 Reload mode

bit5

OUTL

TOT pin output level select bit

One-shot mode (RELD=0) Reload mode (RELD=1)

0

High rectangular wave output

during counting

Low toggle output at starting reload timer

1

Low rectangular wave output

during counting

High toggle output at starting reload timer

bit6

OUTE

TOT pin output enable bit

Pin function

0 General-purpose I/O port

1 TOT output