269

CHAPTER 15 WATCH TIMER

■ Cycle of Clock Supply

The watch timer supplies an operation clock to the oscillation stabilization wait time timer of the subclock

and the watchdog timer. Table 15.1-2 shows the cycles of clocks supplied from the watch timer.

Note:

The frequency of the subclock (SCLK) is a value for 2 division/4 division of the clock inputted to the

low-speed oscillation pin (X0A and X1A) or the internal CR oscillation clock.

The division ratio is set by the SCDS bit of the PLL/subclock control register (PSCCR).

When using the internal CR oscillation clock, see "CHAPTER 6 CLOCK SUPERVISOR". Please con-

sider the frequency difference of built-in CR oscillation when you use built-in CR oscillation clock as a

sub-clock.

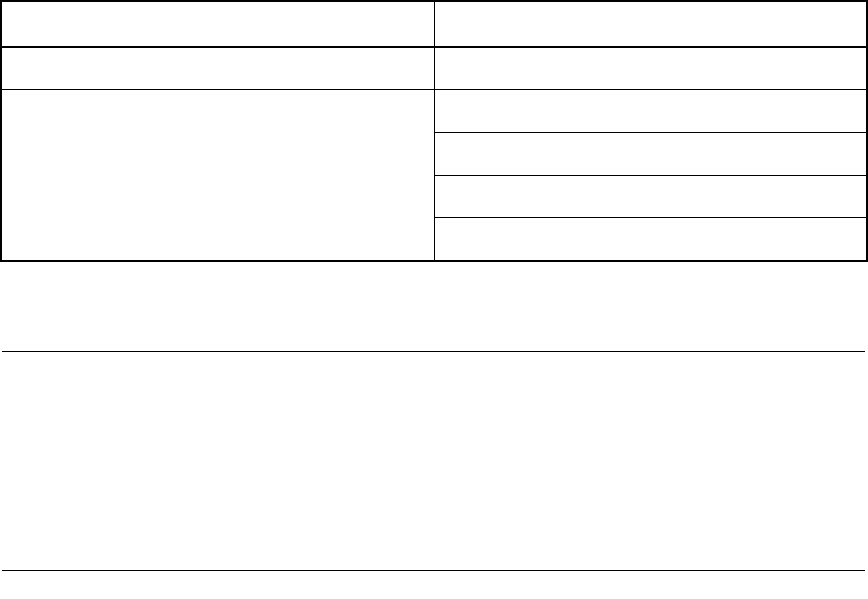

Table 15.1-2 Cycle of Clock Supplied from Watch Timer

Where to Supply Clock Clock Cycle

Timer for oscillation stabilization wait time of subclock

2

14

/SCLK(4.000 s)

Watchdog timer

2

10

/SCLK(125 ms)

2

13

/SCLK(1.000 s)

2

14

/SCLK(2.000 s)

2

15

/SCLK(4.000 s)

SCLK: Subclock frequency

The parenthesized values are provided when the subclock operates at 8.192 kHz.