229

CHAPTER 13 16-Bit I/O TIMER

13.5 Explanation of Operation of 16-bit Free-run Timer

After a reset, the 16-bit free-run timer starts incrementing from "0000

H

". The counter

value of the 16-bit free-run timer is the base time of the input capture.

■ Explanation of Operation of 16-bit Free-run Timer

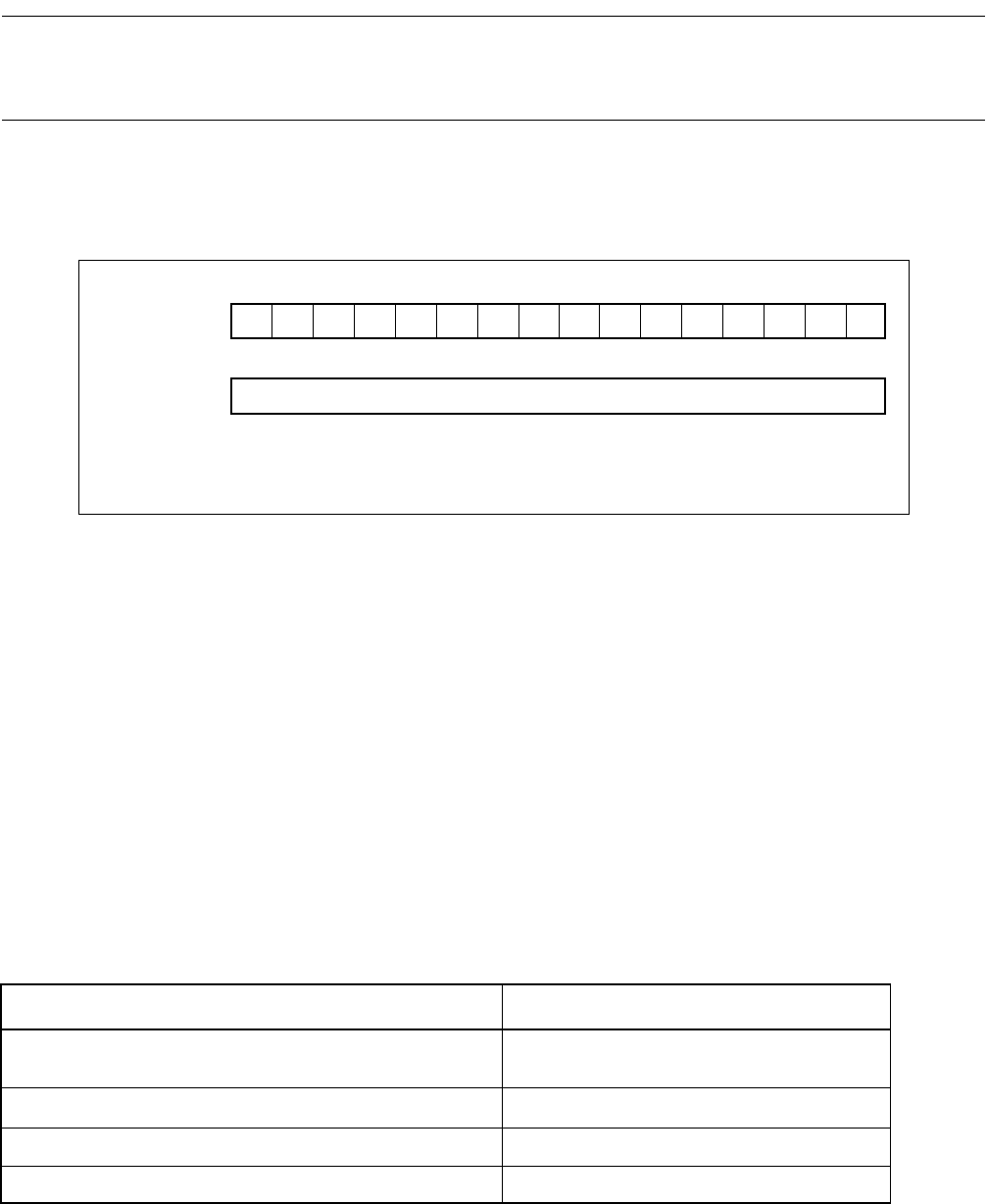

Operation of the 16-bit free-run timer requires the setting shown in Figure 13.5-1 .

Figure 13.5-1 Setting of 16-bit Free-run Timer

[Setting of counter value in 16-bit free-run timer]

• Because the timer operation is enabled (TCCSL:STOP=0) after a reset, the 16-bit free-run timer starts

incrementing from the counter value "0000

H

".

• When setting the counter value of the 16-bit free-run timer, disable the operation of the 16-bit free-run

timer (TCCSL:STOP=1), set the value that starts counting to the timer data register, enable the timer

operation (TCCSL:STOP=0).

[Generation of overflow and interrupt request]

• When overflow ("FFFF

H

" → "0000

H

") occurs in the 16-bit free-run timer, the timer overflow generation

flag is set to "1" (TCCSL:IVF) and starts incrementing from "0000

H

".

• When the timer overflow interrupt request is enabled (TCCSL:IVFE=1), the interrupt request is

occurred.

[Clear factor of counter value and clear timing]

Table 13.5-1 shows the clear factor and clear timing of the 16-bit free-run timer.

0

STOP

−

CLK1 CLK0

CLR

IVF

IVFE

TCDT

TCCSH/TCCSL

bit15 14 13 12 11 10 9 bit8 bit7 654321bit0

0

CLK2

ECKE

−−−−−−−

0

❍

: Used bit

✕

: Undefined bit

0 : Setting to "0"

Counter value of 16-bit free-run timer

❍

❍

❍❍ ❍

❍

✕✕✕

✕

✕✕

✕

Table 13.5-1 Clear Factor of Counter Value and Clear Timing

Clear factor Clear timing

When "1" to timer clear bit of timer control status register (TCCSL:

CLR)

Synchronize with generation of factor

Write "0000

H

" to timer data register during stopping

Synchronize with generation of factor

Reset Synchronize with generation of factor

Timer overflow Synchronize with count timing