189

CHAPTER 11 TIMEBASE TIMER

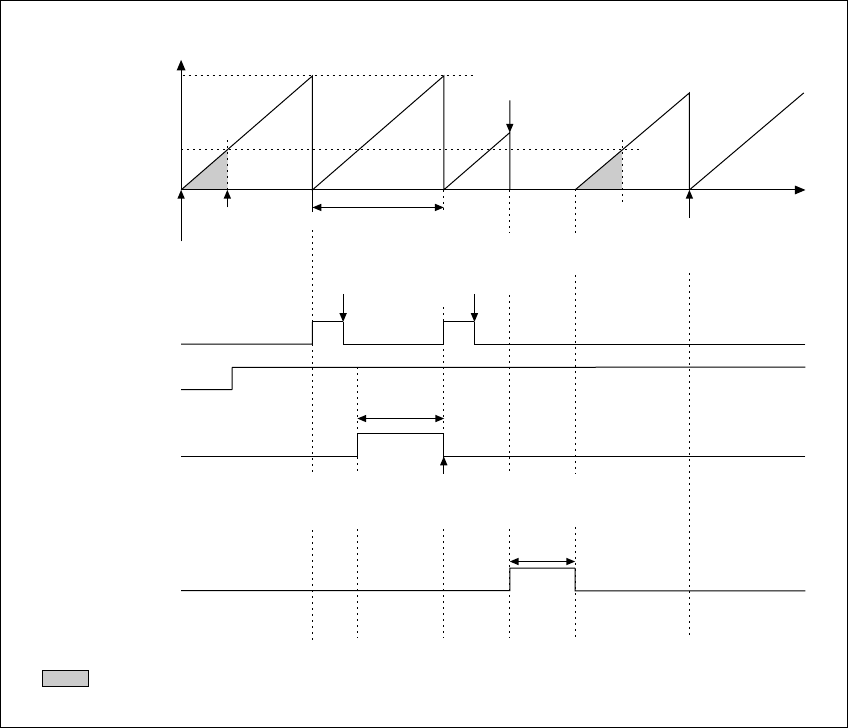

At transition to the stop mode, the timebase timer counter is cleared to stop counting up. At return from the

stop mode, the timebase timer counts the oscillation stabilization wait time of the main clock.

Figure 11.5-2 Example of Operation for Timebase Timer

HCLK

3FFFFH

00000H

: Oscillation stabilization waiting time

: Oscillation clock

Cancellation of sleep at interval interrupt

of timebase timer

Counter value

Clear by transferring to

stop mode

Interval cycle

(TBTC: TBC1: TBC0 = 11

B

)

Start CPU

operation

Power-on reset

TBOF bit

TBIE bit

STP bit

(LPMCR register)

Stop

Clear by interrupt process

Sleep

SLP bit

(LPMCR register)

Counter clear

(TBTC: TBR = 0)

Oscillation

stabilization

waiting overflow

When set the interval time select bit (TBTC:TBC1, TBC0) to "11

B

"(2

19

/HCLK)