397

CHAPTER 20 LIN-UART

20.4.3 Serial Status Register (SSR)

This register checks the transmission and reception status and error status, and

enables and disables the transmission and reception interrupts.

■ Serial Status Register (SSR)

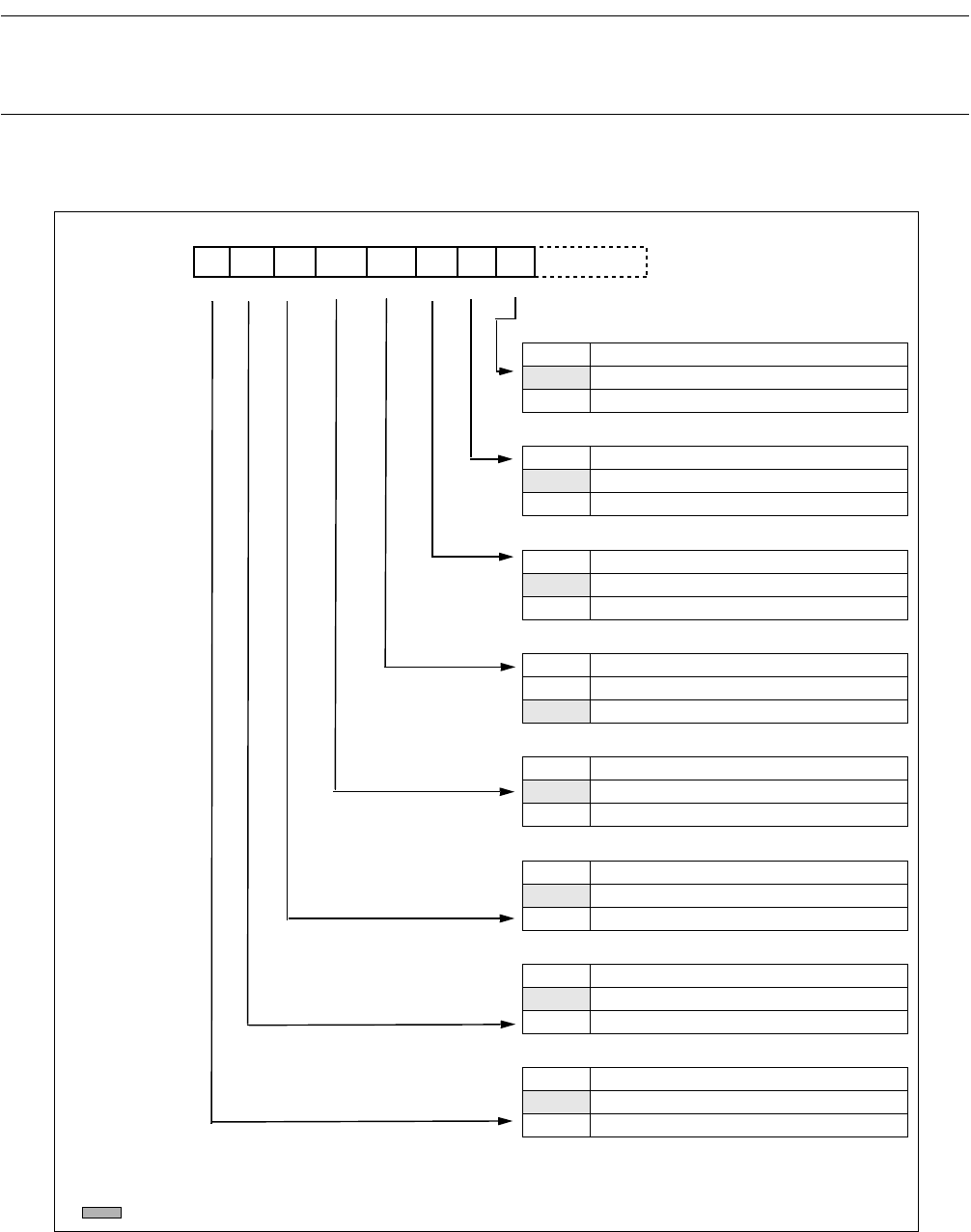

Figure 20.4-4 Configuration of the Serial Status Register (SSR)

PE

ORE

FRE RDRF TDRE

BDS RIE

TIE

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

R R R R R R/W R/W R/W

00001000

B

S

SR0:000023

H

S

SR1:00002B

H

bit7 bit0

R/W : Read/Write

R : Read only

: Initial value

bit8

TIE Transmission interrupt request enable bit

0 Disables transmission interrupt

1 Enables transmission interrupt

bit9

RIE Reception interrupt request enable bit

0 Disables reception interrupt

1 Enables reception interrupt

bit10

BDS Transfer direction selection bit

0 LSB first (transfer from lowest bit)

1 MSB first (transfer from highest bit)

bit11

TDRE Transmission data empty flag bit

0 Transmission data register is full.

1 Transmission data register is empty.

bit12

RDRF Reception data full flag bit

0 Reception data register is empty

1 Reception data register is full

bit13

FRE Framing error flag bit

0 No framing error occurred

1 A framing error occurred

bit14

ORE Overrun error flag bit

0 No overrun error occurred

1 An overrun error occurred

bit15

PE Parity error flag bit

0 No parity error occurred

1 A parity error occurred

Initial value

Address