7

CHAPTER 1 OVERVIEW

■ Features

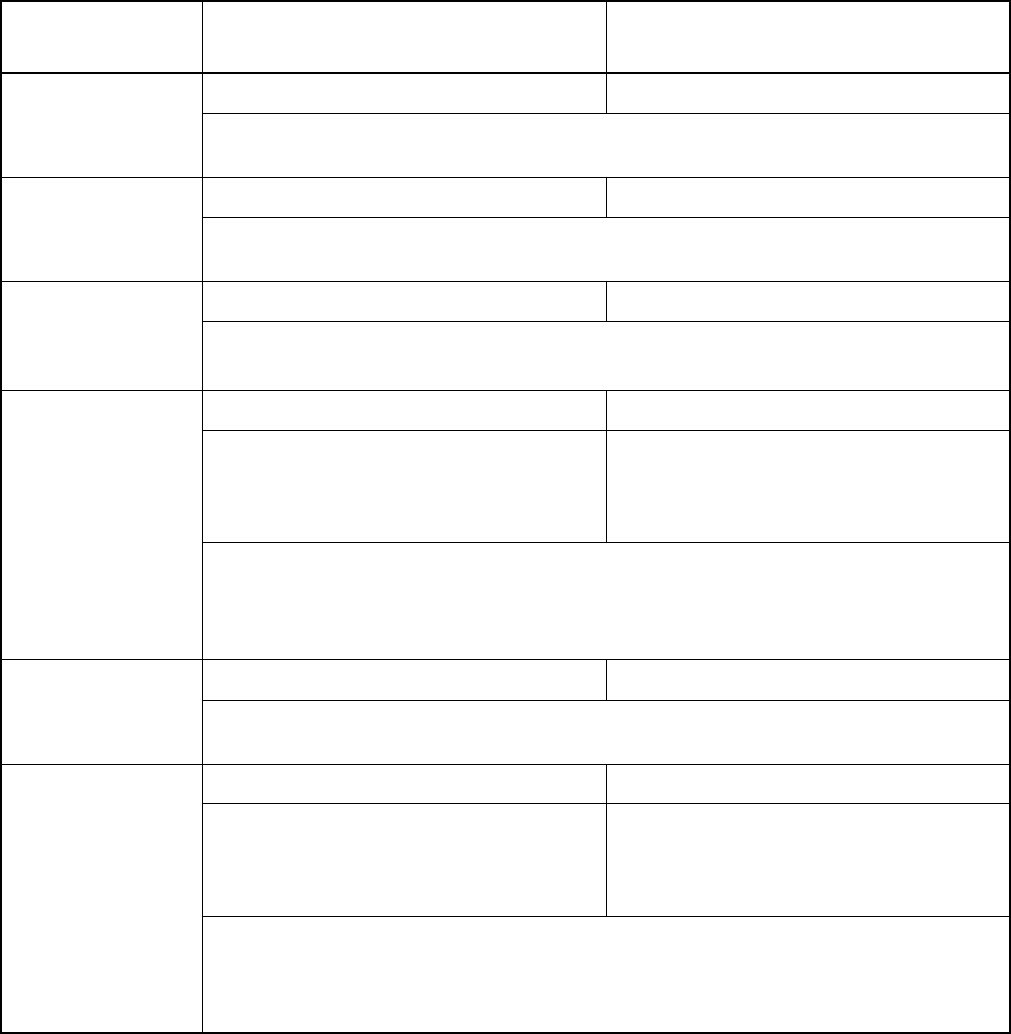

Table 1.1-3 MB90360 Features (1/2)

Features

MB90F362/T(S), MB90362/T(S)

MB90F367/T(S), MB90367/T(S)

MB90V340A-101, MB90V340A-102

MB90V340A-103, MB90V340A-104

UART 2 channels 5 channels

Wide range of baud rate settings using a dedicated reload timer

LIN functionality working either as LIN master or LIN slave device

A/D converter 16 channels 24 channels

10-bit or 8-bit resolution

Conversion time: Minimum 3 µs include sample time (per one channel)

16-bit reload timer

2 channels 4 channels

Operation clock frequency: fsys/2

1

, fsys/2

3

, fsys/2

5

(fsys=System clock freq.)

Support External Event Count function

16-bit I/O timer

1 channel 4 channels

I/O timer 0 (clock input FRCK0)

corresponding ICU 0/1/2/3.

I/O timer 0 (clock input FRCK0) corresponds

to ICU 0/1/2/3, OCU 0/1/2/3

I/O timer 1 (clock input FRCK1) corresponds

to ICU 4/5/6/7, OCU 4/5/6/7

Signal an interrupt when overflowing

Supports Timer Clear when a match with Output Compare (Channel 0, 4)

Operation clock freq.: fsys/2

1

, fsys/2

2

, fsys/2

3

, fsys/2

4

, fsys/2

5

, fsys/2

6

, fsys/2

7

(fsys=System clock freq.)

16-bit input capture

4 channels 8 channels

Maintains I/O timer value by pin input (rising edge, falling edge, or both edges) and generates

interrupt.

8-/16-bit PPG

2 channels 8 channels

Supports 8-bit and 16-bit operation modes

Four 8-bit reload counter

Four 8-bit reload registers for L pulse width

Four 8-bit reload registers for H pulse width

Supports 8-bit and 16-bit operation modes

Sixteen 8-bit reload counter

Sixteen 8-bit reload registers for L pulse width

Sixteen 8-bit reload registers for H pulse width

A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler

plus 8-bit reload counter

Operation clock freq.: fsys, fsys/2

1

, fsys/2

2

, fsys/2

3

, fsys/2

4

or 102.4 µs fosc=@5MHz

(fsys=system clock frequency, fosc=oscillation clock frequency)