60

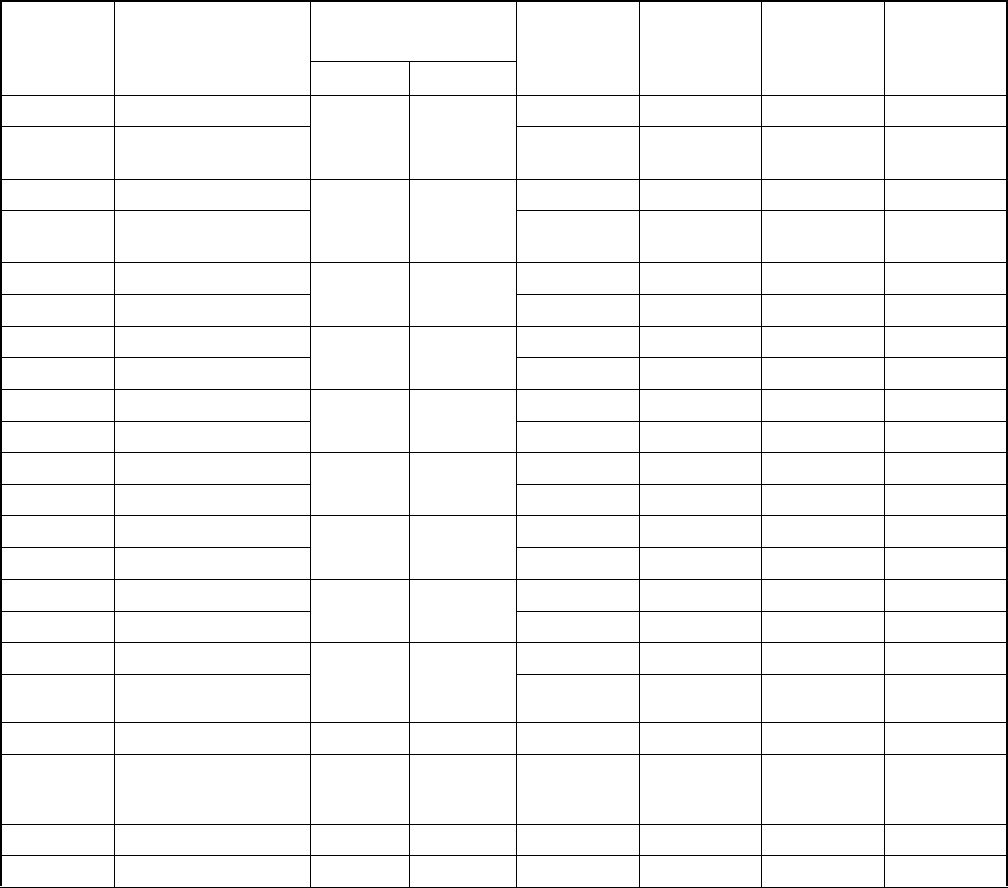

CHAPTER 3 INTERRUPTS

INT 25

Timebase timer 3

ICR07

0000B7

H

FFFF98

H

FFFF99

H

FFFF9A

H

Unused

INT 26

External interrupt

8 to 11

FFFF94

H

FFFF95

H

FFFF96

H

Unused

INT 27

Watch timer

ICR08

0000B8

H

FFFF90

H

FFFF91

H

FFFF92

H

Unused

INT 28

External interrupt

12 to 15

FFFF8C

H

FFFF8D

H

FFFF8E

H

Unused

INT 29

A/D converter

ICR09

0000B9

H

FFFF88

H

FFFF89

H

FFFF8A

H

Unused

INT 30

I/O timer 0 FFFF84

H

FFFF85

H

FFFF86

H

Unused

INT 31

Reserved

ICR10

0000BA

H

FFFF80

H

FFFF81

H

FFFF82

H

Unused

INT 32

Reserved FFFF7C

H

FFFF7D

H

FFFF7E

H

Unused

INT 33

Input capture 0 to 3

ICR11

0000BB

H

FFFF78

H

FFFF79

H

FFFF7A

H

Unused

INT 34

Reserved FFFF74

H

FFFF75

H

FFFF76

H

Unused

INT 35 UART 0 reception

ICR12

0000BC

H

FFFF70

H

FFFF71

H

FFFF72

H

Unused

INT 36 UART 0 transmission

FFFF6C

H

FFFF6D

H

FFFF6E

H

Unused

INT 37 UART 1 reception

ICR13

0000BD

H

FFFF68

H

FFFF69

H

FFFF6A

H

Unused

INT 38 UART 1 transmission

FFFF64

H

FFFF65

H

FFFF66

H

Unused

INT 39

Reserved

ICR14

0000BE

H

FFFF60

H

FFFF61

H

FFFF62

H

Unused

INT 40

Reserved FFFF5C

H

FFFF5D

H

FFFF5E

H

Unused

INT 41 Flash memory

ICR15

0000BF

H

FFFF58

H

FFFF59

H

FFFF5A

H

Unused

INT 42 Delayed interrupt

generation module

FFFF54

H

FFFF55

H

FFFF56

H

Unused

INT 43

-- -- --

FFFF50

H

FFFF51

H

FFFF52

H

Unused

.

.

.

-- -- --

.

.

.

.

.

.

.

.

.

.

.

.

INT 254

-- -- --

FFFC04

H

FFFC05

H

FFFC06

H

Unused

INT 255

-- -- --

FFFC00

H

FFFC01

H

FFFC02

H

Unused

*: When PCB is FF

H

, the vector area for the CALLV instruction overlaps that for INT #vct8 (#0 to #7). Care must be taken

when using the CALLV instruction.

Table 3.2-1 Interrupt Vector (2/2)

Interrupt

request

Interrupt cause

Interrupt control

register

Vector

address

lower

Vector

address

middle

Vector

address

upper

Mode

register

Number Address