385

CHAPTER 20 LIN-UART

■ LIN-UART interrupt and EI

2

OS

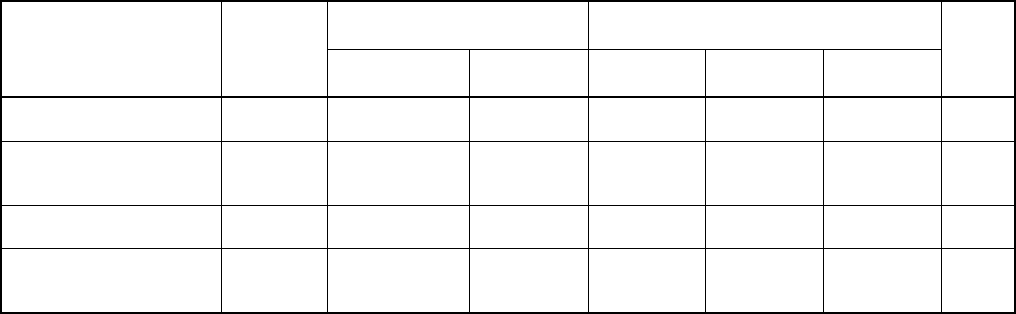

Table 20.1-4 LIN-UART Interrupt and EI

2

OS

Channel Interrupt

number

Interrupt control register Vector table address

EI

2

OS

Register name Address Lower Upper Bank

LIN-UART0 reception #35(23

H

) ICR12 0000BC

H

FFFF70

H

FFFF71

H

FFFF72

H

*1

LIN-UART0

transmission

#36(24

H

) ICR12 0000BC

H

FFFF6C

H

FFFF6D

H

FFFF6E

H

*2

LIN-UART1 reception #37(25

H

) ICR13 0000BD

H

FFFF68

H

FFFF69

H

FFFF6A

H

*1

LIN-UART1

transmission

#38(26

H

) ICR13 0000BD

H

FFFF64

H

FFFF65

H

FFFF66

H

*2

*1: EI

2

OS service is usable if the other interrupt (s) which shares the ICR12 to ICRB and same interrupt vector is (are) not

enabled. Detection of receive errors is possible and stop function for EI

2

OS service is supported.

*2: EI

2

OS service is usable if the other interrupt (s) which shares the ICR12 to ICRB and same interrupt vector is (are) not

enabled.