445

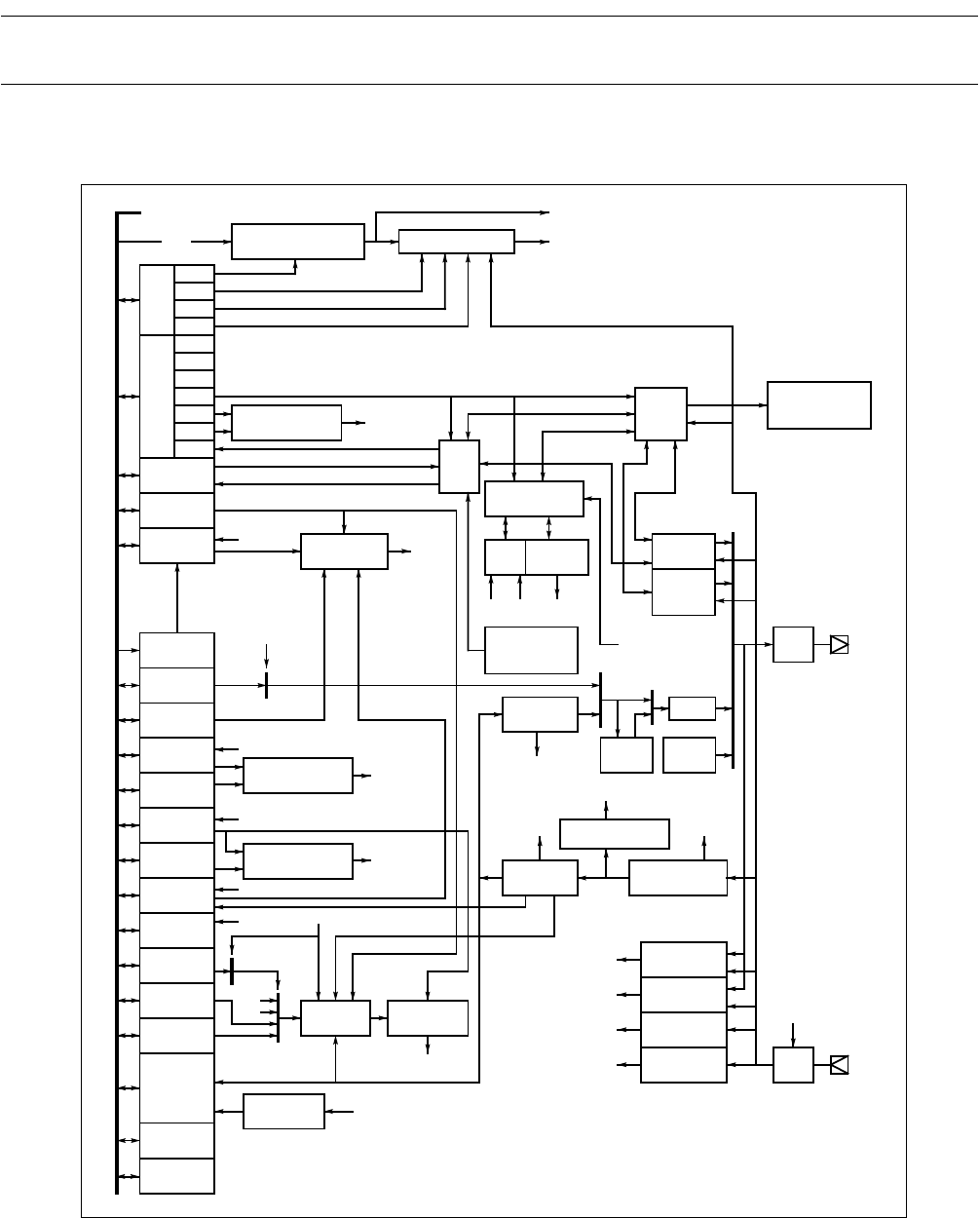

21.2 Block Diagram of CAN Controller

Figure 21.2-1 shows a block diagram of the CAN controller.

■ Block Diagram of CAN Controller

Figure 21.2-1 Block Diagram of CAN Controller

F

2

MC-16LX bus

PSC

TS1

RSJ

TOE

TS

RS

HALT

NIE

NT

NS1, 0

BTR

CSR

Clock

Prescaler

1 to 64 frequency division

Bit timing generation SYNC, TSEG1, TSEG2

TQ (Operating clock)

Node status change

interrupt generation

Node status

change interrupt

Error

control

RTEC

BVALR

TREQR

Transmitting/

receiving sequencer

Data

counter

Acceptance

filter control

Bus state

machine

TDLC RDLC IDSEL

Error frame

generation

Overload

frame

generation

BITER, STFER,

CRCER, FRMER,

ACKER

ARBLOST

IDLE, SUSPND,

transmit, receive,

ERR, OVRLD

Output

driver

TX

TBFx clear

Transmitting buffer

x decision

TBFx

TCANR

TRTRR

RFWTR

TCR

TIER

RCR

RIER

RRTRR

ROVRR

AMSR

AMR0

TBFx

TBFx, set, clear

Transmission complete

interrupt generation

Transmission

complete

interrupt

Reception

complete

interrupt

RBFx, set

Reception complete

interrupt generation

RBFx, TBFx, set, clear

RBFx, set

IDSEL

0

1

Acceptance

filter

Receiving buffer

to decision

RBFx

IDR0 to 15,

DLCR0 to 15,

DTR0 to 15,

RAM

RAM address

generation

RBFx, TBFx, RDLC, TDLC, IDSEL

Transmission

shift register

TDLC

CRC

generation

Stuffing

ACK

generation

Receive shift

register

RDLC

Destuffing/stuffing

error check

CRCER

CRC generation/error

check

STFER

Arbitration

check

Bit error

check

Form error

check

Acknowledgment

error check

ARBLOST

BITER

ACKER

FRMER

Input

latch

RX

PH1

LEIR

IDER

TS2

AMR1