213

CHAPTER 13 16-Bit I/O TIMER

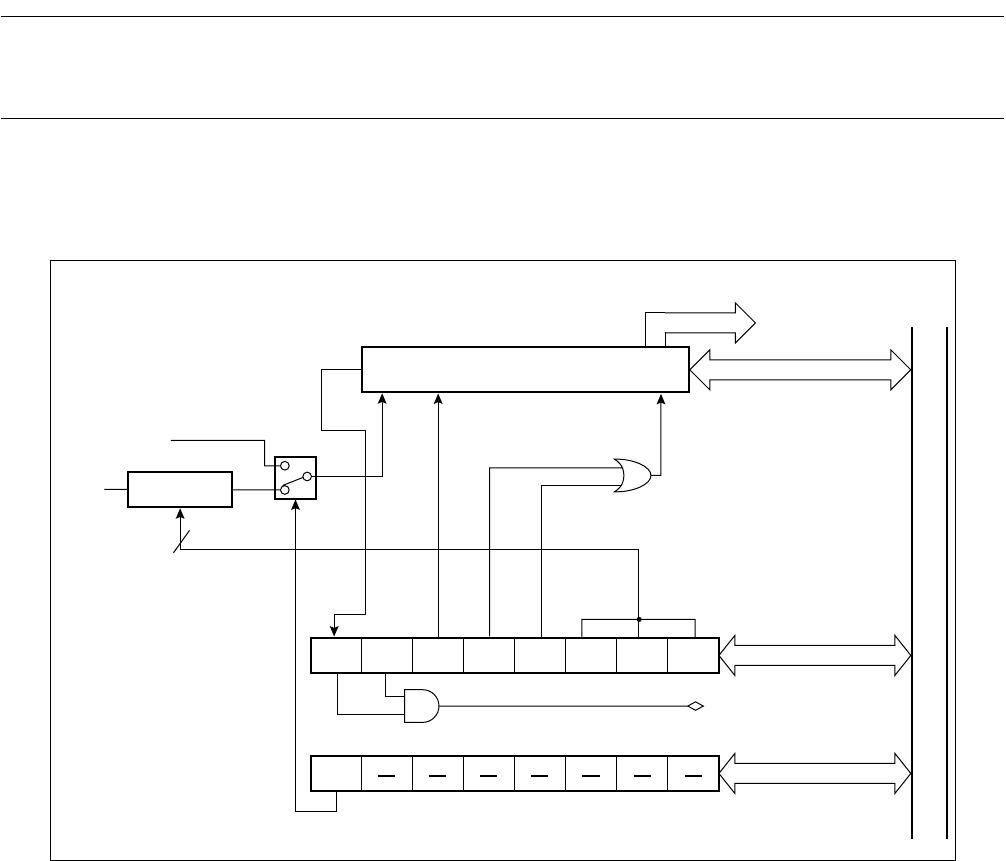

13.2.1 Block Diagram of 16-bit Free-run Timer

The MB90360 series contains 1 channel of the 16-bit free-run timer, and it consists of

the following block.

■ Block Diagram of 16-bit Free-run Timer

Figure 13.2-2 Block Diagram of 16-bit Free-run Timer

●

Prescaler

The prescaler divides the frequency of the machine clock to supply a count clock to the 16-bit counter. Any

of eight count clock cycles can be selected by setting the timer control status register (TCCSL: CLK2 to

CLK0).

●

Timer data register (TCDT)

The timer data register can read the counter value of the 16-bit free-run timer. During stopping of the 16-bit

free-run timer, the counter value can be set by writing the counter value to the TCDT.

●

Timer control status register (TCCSH, TCCSL)

The timer control status register (upper and lower) selects the count clock and the condition for clearing the

counter, clears the counter, enables the count operation and interrupt request, checks the overflow

generation flag.

STOP

IVF CLR CLK1CLK2 CLK0IVFE

Reserved

CLK

STOP

CLR

ECKE

3

OF

φ

Timer control status

register (Lower)

(TCCSL0)

Timer data register

(TCDT0)

Output count value to

input capture

Free-run timer overflow

interrupt request

External clock

(FRCK0)

Prescaler

Internal data bus

Timer control status

register (Upper)

(TCCSH0)

16-bit counter

φ : Machine clock

OF : Overflow