251

CHAPTER 14 16-BIT RELOAD TIMER

14.4 Interrupts of 16-bit Reload Timer

The 16-bit reload timer generates an interrupt request when the 16-bit timer register

(TMR) underflows.

■ Interrupts of 16-bit Reload Timer

When the value of the TMR is decremented from "0000

H

" to "FFFF

H

" during the TMR count operation, an

underflow occurs. When an underflow occurs, the underflow generating flag bit in the timer control status

register (TMCSR:UF) is set to l. When an underflow interrupt is enabled (TMCSR:INTE = 1), an interrupt

request is generated.

■ Correspondence between 16-bit Reload Timer Interrupt and EI

2

OS

■ EI

2

OS Function of 16-bit Reload Timer

The 16-bit reload timers 2 and 3 correspond to the EI

2

OS function. An underflow in the TMR starts the

EI

2

OS.

However, the EI

2

OS is available only when other resources sharing the interrupt control register (ICR) do

not use interrupts. The 16-bit reload timers 2 and 3 share the ICR04. When using the EI

2

OS in the 16-bit

reload timers 2 and 3, it is necessary to disable the interrupt of the 16-bit reload timer sharing the interrupt

control register.

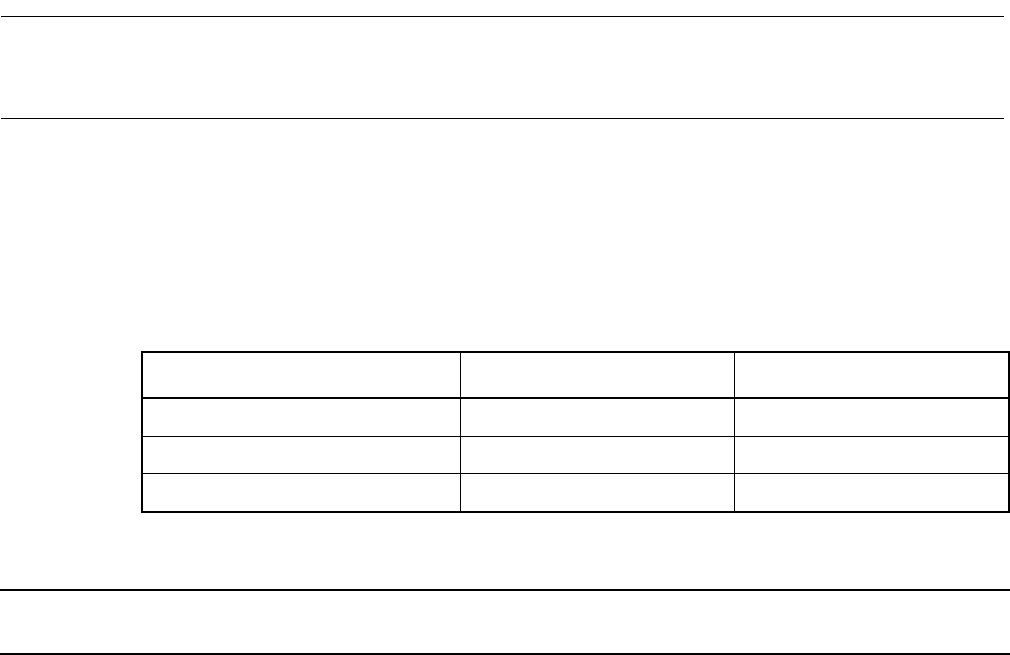

Table 14.4-1 Interrupt Control Bits and Interrupt Factors of 16-bit Reload Timer

16-bit Reload Timer 2 16-bit Reload Timer 3

Interrupt request flag bit TMCSR2: UF TMCSR3: UF

Interrupt request enable bit TMCSR2: INTE TMCSR3: INTE

Interrupt factor Underflow in TMR2 Underflow in TMR3

Reference: For details of the interrupt number, interrupt control register, and interrupt vector address, see "CHAPTER

3 INTERRUPTS".