98

CHAPTER 5 CLOCKS

5.3 Clock Selection Register (CKSCR)

The clock selection register (CKSCR) is used to switch among the main clock, PLL

clocks and subclock, also used to select an oscillation stabilization wait interval and a

PLL clock multiplier.

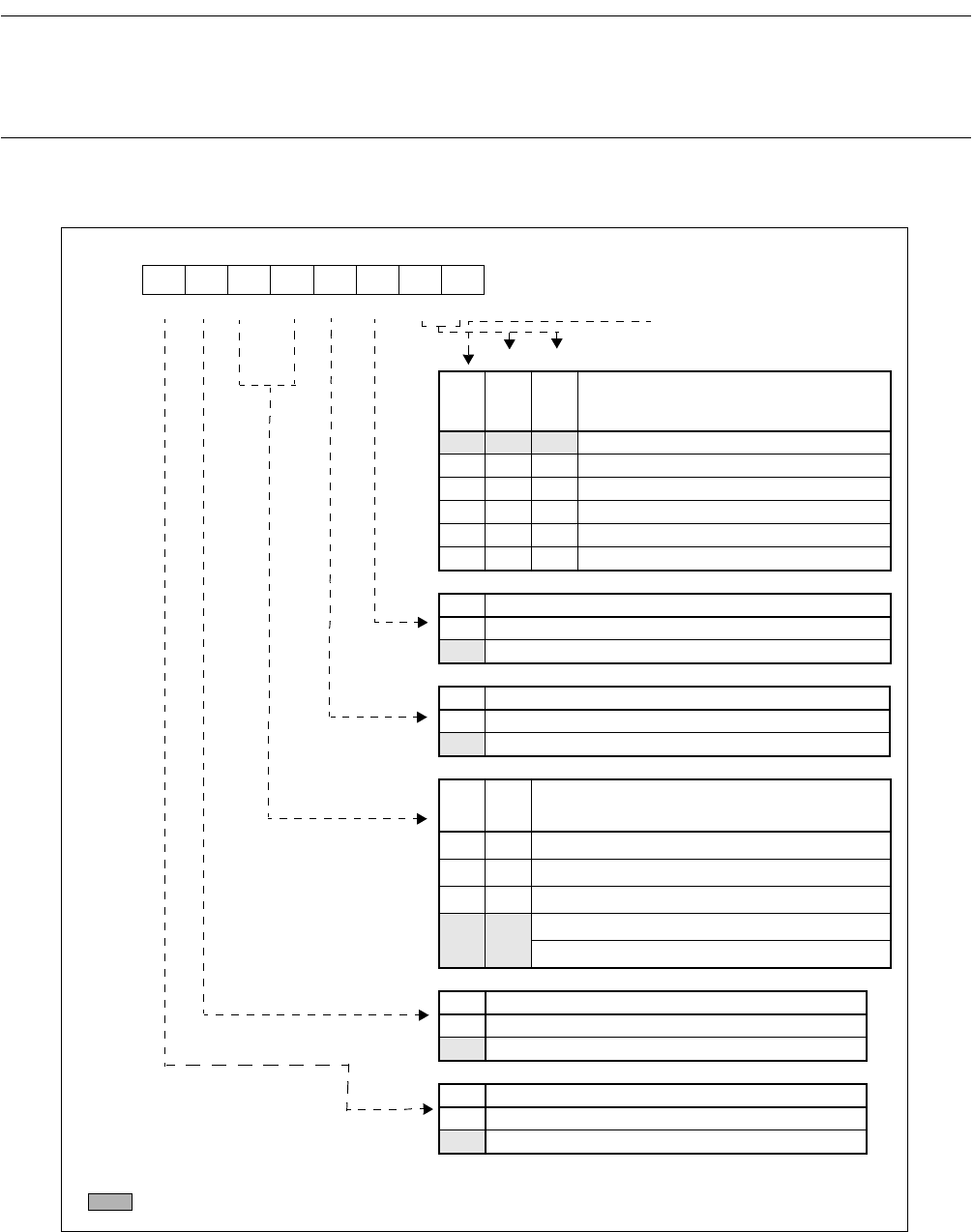

■ Configuration of the Clock Selection Register (CKSCR)

Figure 5.3-1 Configuration of the Clock Selection Register (CKSCR)

bit9 bit8

CS2 CS1 CS0

Multiplication rate select bit

Parenthesized values are examples calculated at

an oscillation clock (HCLK) frequency of 4 MHz.

0 0 01 × HCLK (4 MHz)

0012 × HCLK (8 MHz)

0103 × HCLK (12 MHz)

0114 × HCLK (16 MHz)

1106 × HCLK (24 MHz)

1 1 1 Setting disabled

bit10

MCS PLL clock select bit

0 Select PLL clock

1 Select main clock

bit11

SCS Sub clock select bit

0 Select sub clock

1 Select main clock

bit13 bit12

WS1 WS0

Oscillation stabilization wait time select bit

Parenthesized values are examples calculated at an

oscillation clock (HCLK) frequency of 4 MHz.

00

2

10

/HCLK (approx. 256 µs)

01

2

13

/HCLK (approx. 2.05 ms)

10

2

17

/HCLK (approx. 32.77 ms)

1 1

2

15

/HCLK

(

approx.

8.19 ms, other than power-on reset)

2

16

/HCLK

(

approx.

16.38 ms, power-on reset only)

bit14

MCM PLL clock operation bit

0 Operating in PLL clock

1 Operating in main clock or sub clock

bit15

SCM Sub clock operation bit

0 Operating in sub clock

1 Operating in main clock or PLL clock

Address1514131211109 8 Reset value

0000A1

H

SCM MCM WS1 WS0 SCS MCS CS1 CS0

11111100

B

R R R/W R/W R/W R/W R/W R/W

CS2(PSCCR register: bit8)

HCLK : Oscillation clock

R/W : Read/Write

R : Read only

: Reset value