217

CHAPTER 13 16-Bit I/O TIMER

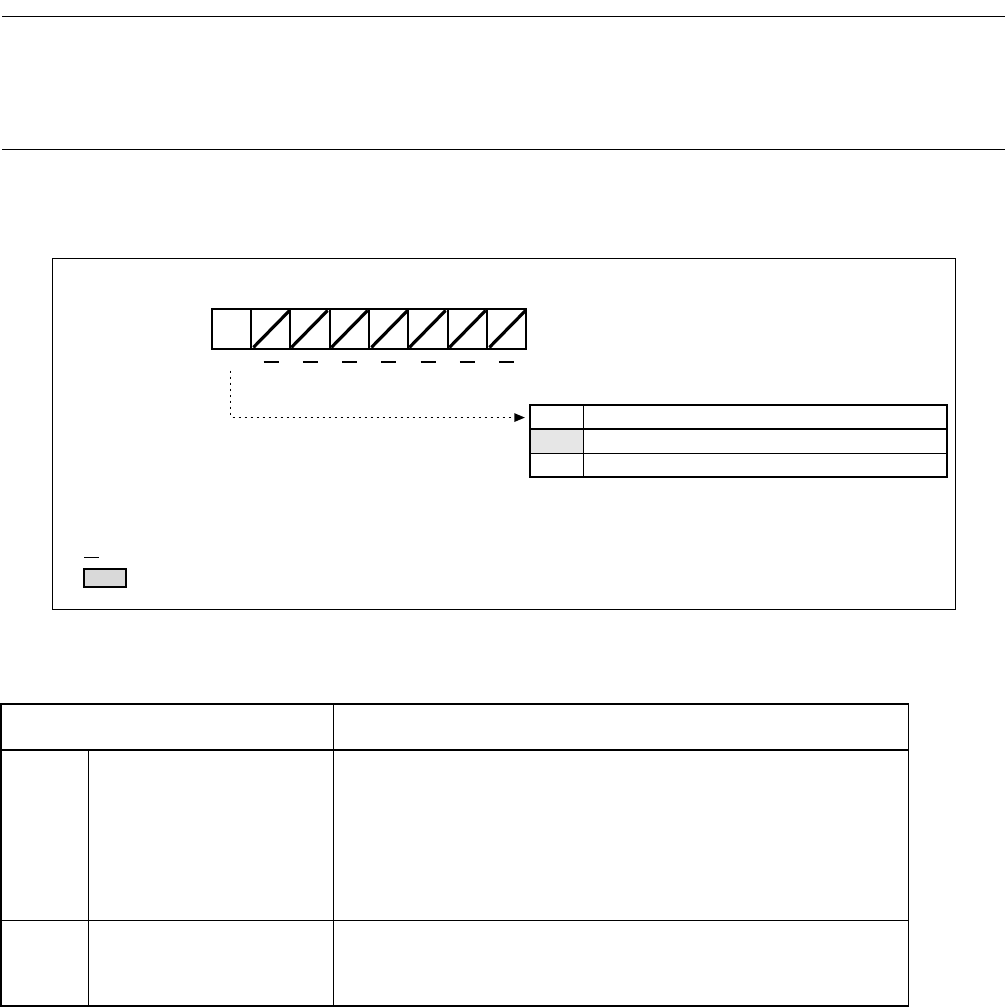

13.3.1 Timer Control Status Register (Upper) (TCCSH)

Timer control status register (upper) selects the count clock and the conditions for

clearing the counter, enables the count operation and interrupt, and checks the

interrupt request flag.

■ Timer Control Status Register (Upper) (TCCSH)

Figure 13.3-1 Timer Control Status Register (Upper) (TCCSH)

TCCSH0 : 007943H

0XXXXXXXB

1213 11 10 9 8

15

14

R/W

R/W

X

ECKE

: Read/Write

: Undefined

: Indetermination

: Reset value

Address

Reset value

bit15

ECKE External clock input enable bit

0 Use the internal clock (prescaler output).

1 Use the external clock (FRCK0 pin input).

Table 13.3-2 Function of Timer Control Status Register (Upper) (TCCSH)

Bit name Function

bit15 ECKE :

External clock input enable bit

This bit selects the count clock of the 16-bit free-run timer.

When set to "1": Use the clock inputted from the external pin FRCK0.

When set to "0": Use the internal clock (clock outputted from the

prescaler).

Note:

Set the ECKE bit during stopping of the free-run timer

(TCCSL:STOP=1).

bit14

to

bit8

Undefined bits

Read: The value is undefined

Write: No effect