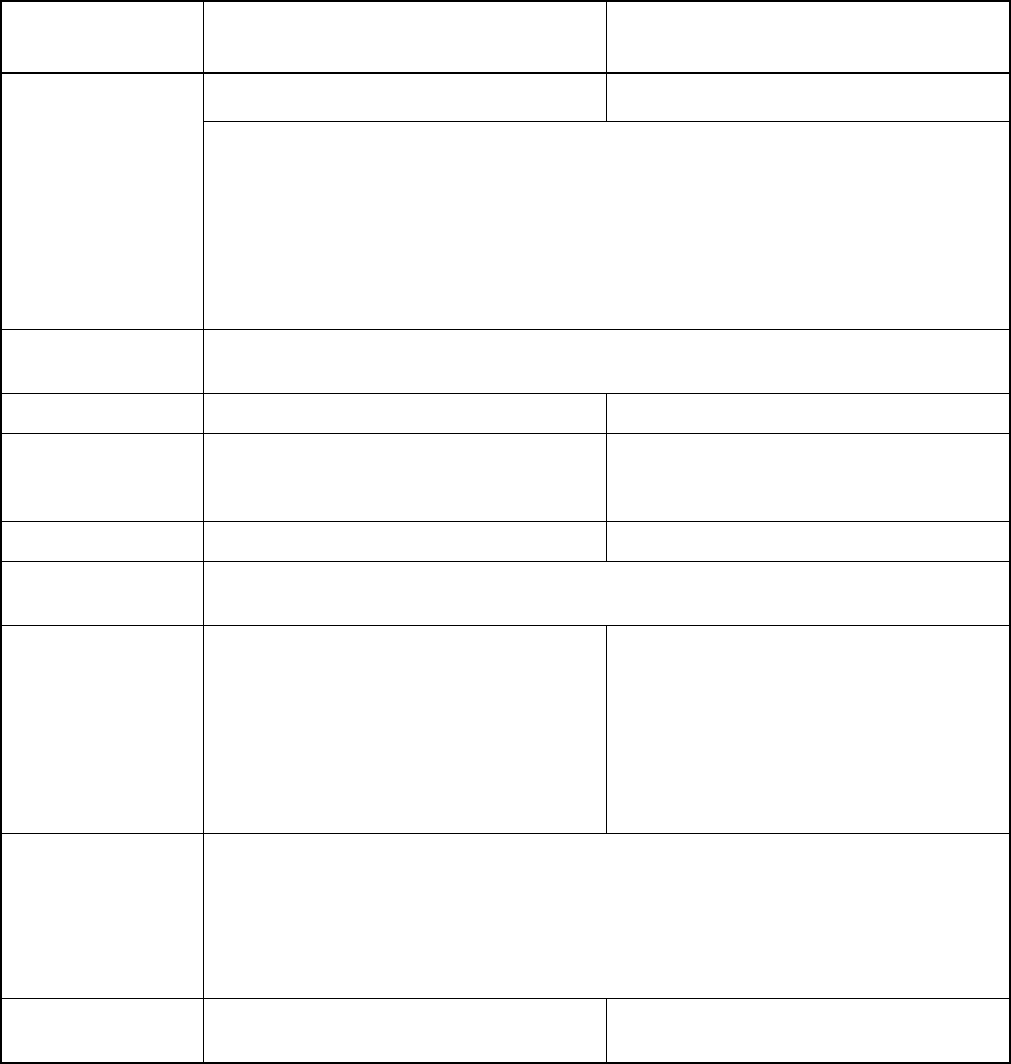

8

CHAPTER 1 OVERVIEW

CAN interface

1 channel

3 channels

Conforms to CAN Specification Version 2.0 Part A and B

Automatic re-transmission in case of error

Automatic transmission responding to Remote Frame

16 message buffers for transmission/reception

Supports multiple messages

Flexible configuration of acceptance filtering:

• Full bit compare/Full bit mask/2 partial bit masks

• Supports up to 1 Mbps communication

External interrupt (8

channels)

Can be programmed edge sensitive or level sensitive

D/A converter - 2 channels

Low voltage/CPU

operation detection

reset

Corresponds to product with T-suffix only -

Clock supervisor MB90F367/T(S), MB90367/T(S) only -

Subclock

(Maximum 100 kHz)

Corresponds to product without T-suffix only

Corresponds to MB90V340A-102/MB90V340A-104 only

I/O port Supports general-purpose I/O (CMOS output):

- 34 ports (product without S-suffix)

- 36 ports (product with S-suffix)

Input level setting:

- Port2, Port4, Port6, Port8: selectable from

CMOS/Automotive level

Supports general-purpose I/O (CMOS output):

- 80 ports (product without S-suffix)

- 82 ports (product with S-suffix)

Input level setting

- Port 0 to Port 3: selectable from CMOS/

Automotive/TTL level

- Port 4 to Port A: selectable from CMOS/

Automotive level

Flash memory

Supports automatic programming, Embedded Algorithm

TM*

, Write/Erase/Erase-Suspend/Resume

commands

A flag indicating completion of the algorithm

Number of erase cycles: 10,000 times

Data retention time: 20 years

Flash Security Feature for protecting the content of the Flash

ROM security Protects the content of ROM (MASK ROM

product only)

-

*:Embedded Algorithm is a registered trademark of Advanced Micro Device Inc.

Table 1.1-3 MB90360 Features (2/2)

Features

MB90F362/T(S), MB90362/T(S)

MB90F367/T(S), MB90367/T(S)

MB90V340A-101, MB90V340A-102

MB90V340A-103, MB90V340A-104