590

APPENDIX

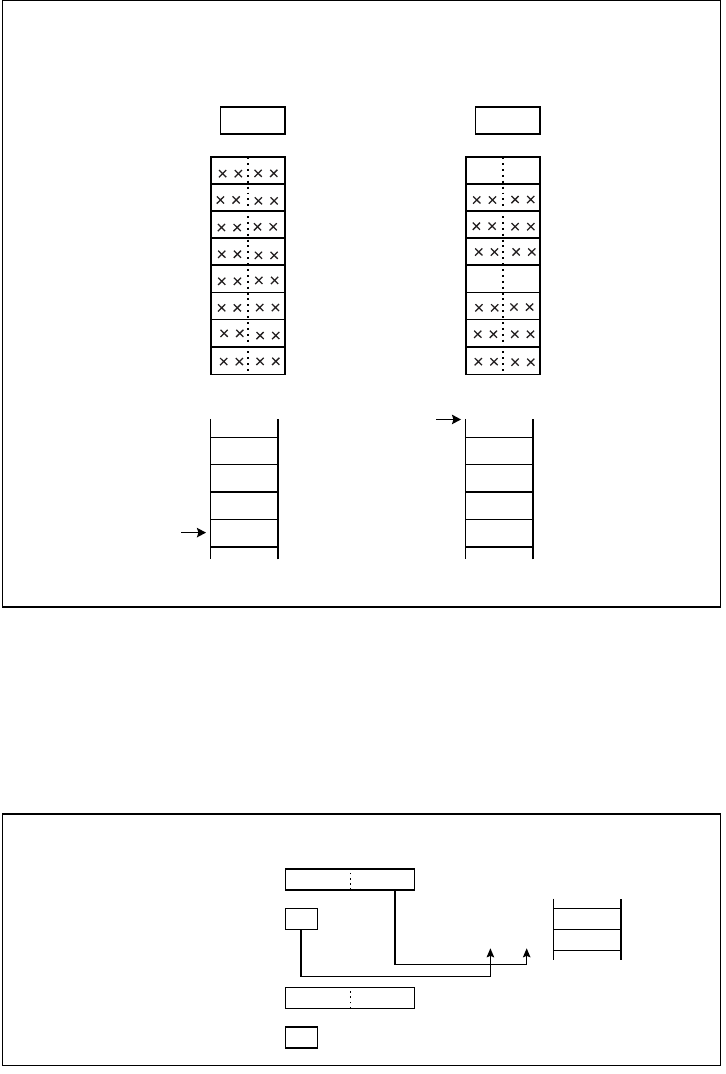

Figure B.4-9 Example of Register List (rlst)

●

Accumulator indirect addressing (@A)

Memory is accessed using the address indicated by the contents of the low-order bytes (16 bits) of the

accumulator (AL). Address bits 16 to 23 are specified by a mnemonic in the data bank register (DTB).

Figure B.4-10 Example of Accumulator Indirect Addressing (@A)

POPW

RW0, RW4

3 4 F ASP

RW0

RW1

RW2

RW3

RW4

RW5

RW6

RW7

0 4

0 3

34FDH

34FCH

34FEH

0 2

0 1

34FBH

34FAHSP

3 4 F ESP

0 1

0 2RW0

RW1

RW2

RW3

RW4

RW5

RW6

RW7

0 3

0 4

0 4

0 3

34FDH

34FCH

34FEH

0 2

0 1

34FBH

34FAH

SP

Before execution

After execution

Memory space

Memory space

(This instruction transfers memory data indicated by the SP to multiple

word registers indicated by the register list.)

MOVW

A, @A

0 7 1 6A

2 5 3 4

DTB F F

E E

0 7 1 6A

F F E E

DTB

B B

B B

BB2535H

BB2534H

Before execution

After execution

Memory space

(This instruction reads data by accumulator indirect addressing and stores it in A.)