298

CHAPTER 16 8-/16-BIT PPG TIMER

16.3.4 PPG Reload Registers (PRLLC/PRLHC, PRLLD/PRLHD)

The value (reload value) from which the PPG down counter starts counting is set in the

PPG reload registers, which are an 8-bit register at Low level and an 8-bit register at

High level.

This section explains the function of PRLLC/PRLHC and PRLLD/PRLHD only. The

PRLLE/PRLHE, PRLLF/PRLHF have the same function as the PRLLC/PRLHC, and the 8-/

16-bit PPG timers E, F are set.

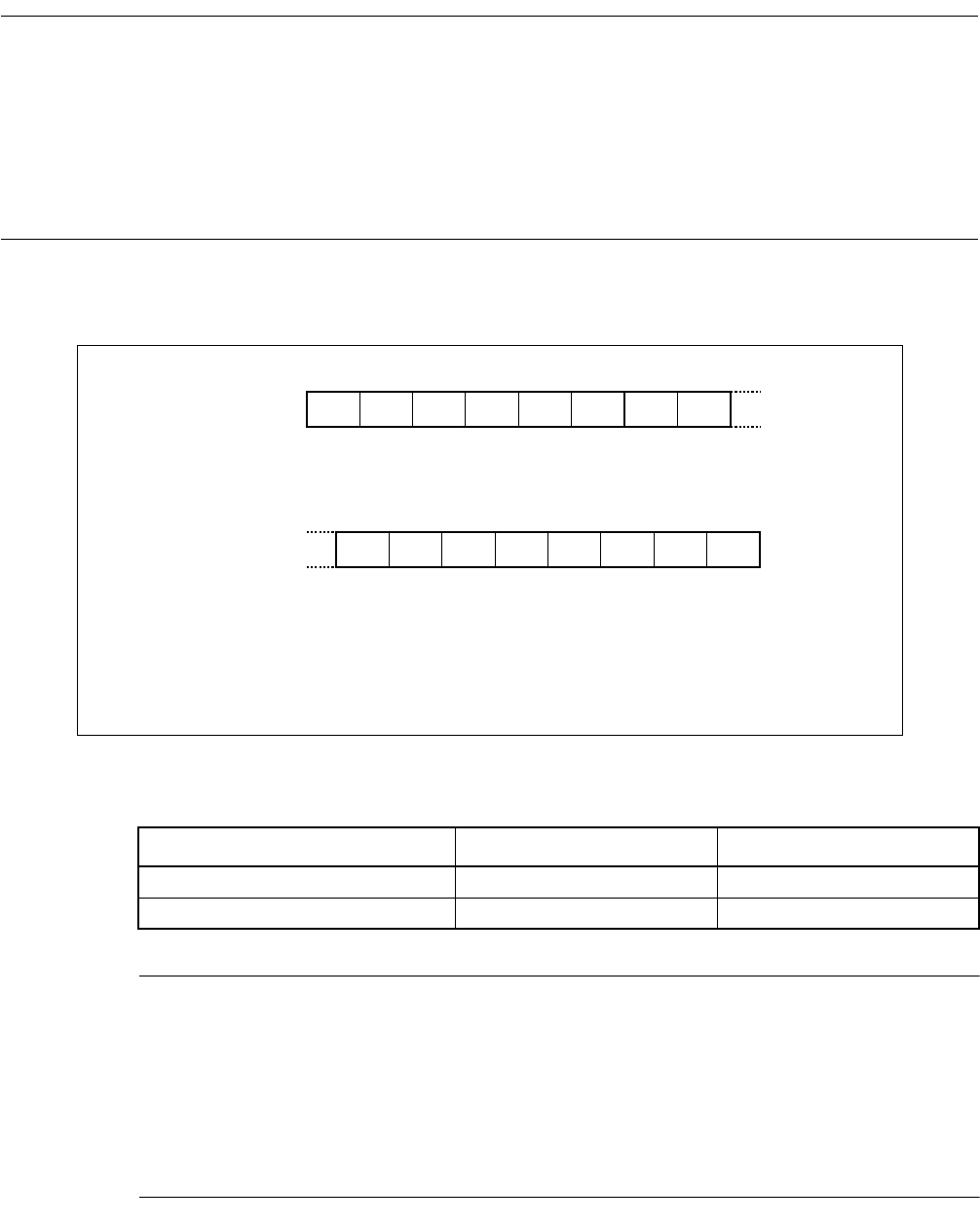

■ PPG Reload Registers (PRLLC/PRLHC, PRLLD/PRLHD)

Figure 16.3-5 PPG Reload Registers (PRLLC/PRLHC, PRLLD/PRLHD)

Table 16.3-5 indicates the functions of the PPG reload registers.

Notes:

• In the 16-bit PPG output operation mode (PPGCD: MD1, MD0="11

B

"), use a long-word instruction to

set the PPG reload registers or the word instruction to set the PPGC and PPGD in this order.

• In the 8 + 8-bit PPG output operation mode (PPGCD: MD1, MD0="01

B

"), set the same value in both the

Low-level and High-level PPG reload registers (PRLLC/PRLHC) of the 8-/16-bit PPG timer C. Setting a

different value in the Low-level and High-level PPG reload registers may cause the 8-/16-bit PPG timer D

to have different PPG output waveforms at each clock cycle.

R/W R/WR/WR/WR/W R/WR/WR/W

D11 D8D9D10D15 D12D13D14

R/W R/WR/WR/WR/W R/WR/WR/W

D3 D0D1D2D7 D4D5D6

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

XXXXXXXX

B

XXXXXXXX

B

Address:

chC PRLHC 007919

H

chD PRLHD 00791B

H

Other channel:

chE PRLHE 00791D

H

chF PRLHF 00791F

H

Address:

chC PRLLC 007918

H

chD PRLLD 00791A

H

Other channel:

chE PRLLE 00791C

H

chF PRLLF 00791E

H

R/W : Read/Write

✕

: Undefined

Reset value

Reset value

Table 16.3-5 Functions of PPG Reload Registers

Function 8-/16-bit PPG Timer C 8-/16-bit PPG Timer D

Retains reload value on Low-level side PRLLC PRLLD

Retains reload value on High-level side PRLHC PRLHD