227

CHAPTER 13 16-Bit I/O TIMER

13.4 Interrupts of 16-bit I/O Timer

The interrupt factors of the 16-bit I/O timer has overflow of the counter value in the 16-

bit free-run timer, trigger edge input to the input capture input pin, and trigger edge

input for the LIN slave baud rate measurement from the LIN-UART.

The EI

2

OS can be started by the interrupt of the input capture.

■ Interrupts of 16-bit I/O Timer

Table 13.4-1 shows interrupt control bits and interrupt factors of 16-bit I/O timer.

●

Timer counter overflow interrupt

When the timer overflow interrupt request is set:

The timer overflow generation flag of the timer control status register is set in the following cases

(TCCSL:IVF=1).

• When overflow ("FFFF

H

" → "0000

H

") occurs at counting up of the 16-bit free-run timer.

When the timer overflow interrupt request occurs:

When the timer overflow interrupt request is set to enable (TCCSL:IVFE=1) if the timer overflow

generation flag is set to "1" (TCCSL:IVF=1), the interrupt request is generated.

●

Input capture Interrupt

When the valid edge set by the input capture pin (ICS:EG) is detected, or when the trigger edge for the LIN

slave baud rate measurement from the LIN-UART is inputted (valid edge must be set to both edges), the

interrupt is shown below.

• The counter value of the detected 16-bit free-run timer is stored to the input capture register.

• The valid edge detection flag of the input capture control status register is set to "1". (ICS: ICP=1)

• When the output of the input capture interrupt request is set to enable (ICS: ICE=1), the interrupt

request is generated.

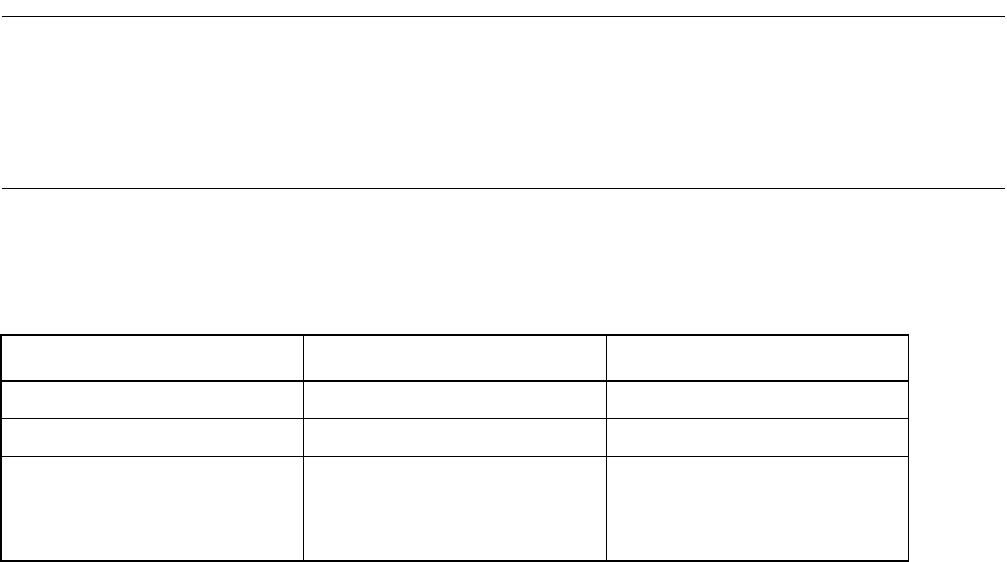

Table 13.4-1 Interrupts of 16-bit I/O Timer

Timer counter overflow interrupt Input capture interrupt

Interrupt request flag TCCSL: IVF ICSnm: ICPn, ICPm

Interrupt request output enable bit TCCSL: IVFE ICSnm: ICEn, ICEm

Interrupt factor

Counter overflow of 16-bit free-run

timer

Valid edge input to the input capture

input pin and trigger edge input for the

LIN slave baud rate measurement

from the LIN-UART

n = 0, 2 m = n+1