130

CHAPTER 7 RESETS

■ Status of Reset Cause Bit and Low Voltage Detection Bit

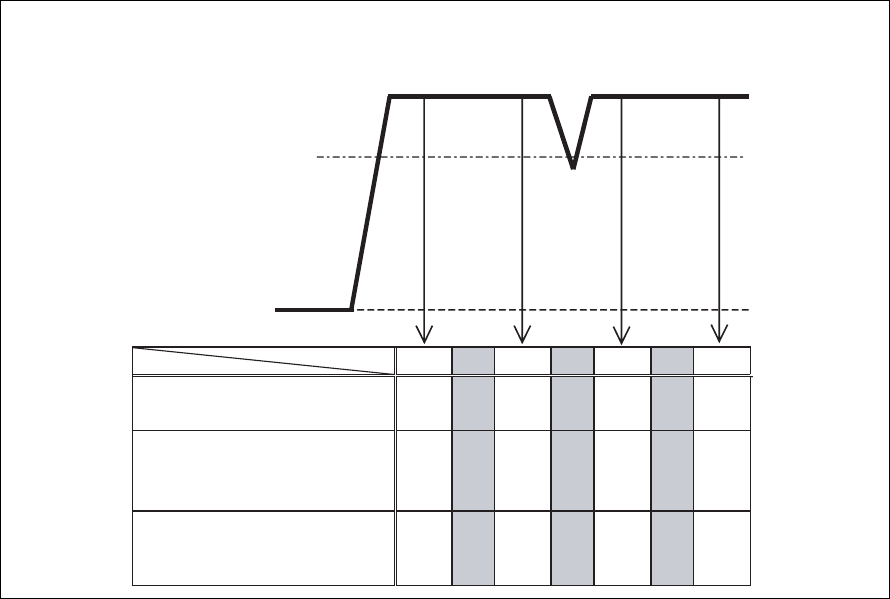

Figure 7.5-3 Status of Reset Cause Bit and Low Voltage Detection Bit

*: The LVRF bit exist in the low voltage/CPU operation detection reset control register (LVRC).

(1) At power-on

Power-on reset bit (PONR) , ERST, and LVRF are set to "1" at power on.

(2) Bit clear

Bit is cleared by reading the WDTC register and by writing "0" to LVRF.

(3) At low voltage detection (4.0 V ± 0.3 V)

The LVRF and ERST bits are set to "1" at low voltage detection of V

CC

= 4.0 V ± 0.3 V.

(4) Bit clear

Bit is cleared by reading the WDTC register and by writing "0" to LVRF.

(1)

(2)

(3)

(4)

1

→

0

→

0

→

0

1

or

0

→

0

→

1

→

0

1

or

0

→

0

→

1

→

0

Vcc

Vcc=4V

Flag status

at power-on

Bit

clear

Flag status at

low voltage

detection (4V)

Bit

clear

PONR bit

(power-on)

ERST bit (external reset

input, CPU operation detection,

or LVRF = 1)

LVRF bit*

(low voltage detection

4V

±

0.3V)