223

CHAPTER 13 16-Bit I/O TIMER

13.3.5 Input Capture Register (IPCP)

Input capture register stores the counter value fetched from 16-bit free-run timer by the

capture operation.

The IPCP register is the 16-bit read-only register and has the input capture registers 0 to

3 (IPCP0 to IPCP3).

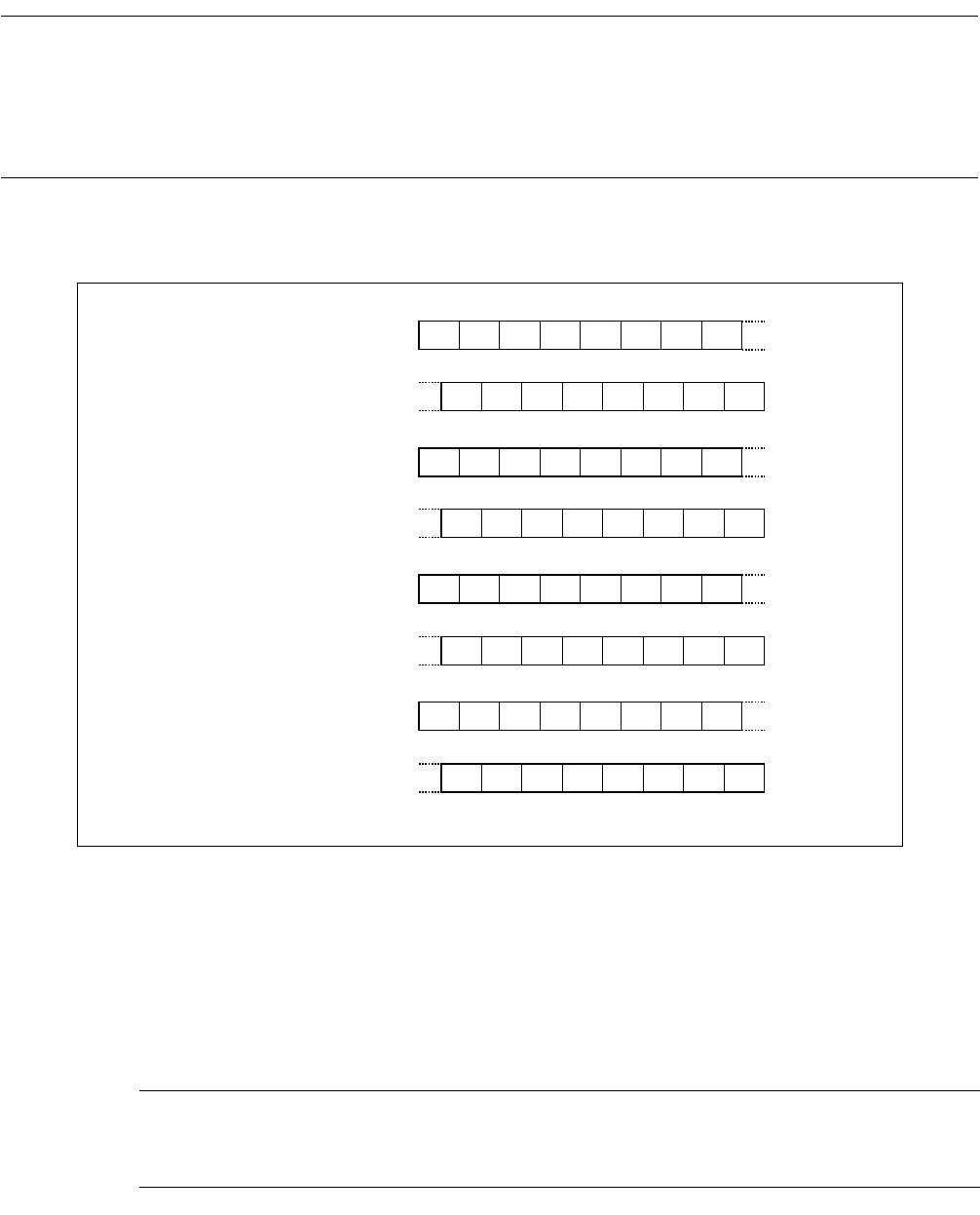

■ Input Capture Register (IPCP)

Figure 13.3-5 Input Capture Register (IPCP)

When the trigger edge of the capture operation (ICSnm: set by EGn1, EGn0 or EGm1, EGm0) is detected

by the IN0 to IN3 pins, the counter value of the 16-bit free-run timer is stored in the input capture registers

0 to 3 corresponding to each pin.

However, the input capture registers 0 and 1 can be selected a signal from the LIN-UART as the input

signal (ICE: selected by IEI bit). See "13.3.6 Input Capture Edge Register (ICE)" for details.

The input capture register can be read, but can not be written.

n =0,2 m = n+1

Note:

Always use a word instruction (MOVW) to read the input capture register.

RRRRRRRR

CP03 CP00CP01CP02CP07 CP04CP05CP06

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

XXXXXXXXB

RRRRRRRR

CP11 CP08CP09CP10CP15 CP12CP13CP14

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

XXXXXXXXB

RRRRRRRR

CP03 CP00CP01CP02CP07 CP04CP05CP06

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

XXXXXXXXB

RRRRRRRR

CP11 CP08CP09CP10CP15 CP12CP13CP14

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

XXXXXXXXB

RRRRRRRR

CP03 CP00CP01CP02CP07 CP04CP05CP06

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

XXXXXXXXB

RRRRRRRR

CP11 CP08CP09CP10CP15 CP12CP13CP14

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

XXXXXXXXB

RRRRRRRR

CP03 CP00CP01CP02CP07 CP04CP05CP06

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

XXXXXXXXB

RRRRRRRR

CP11 CP08CP09CP10CP15 CP12CP13CP14

bit15 bit14 bit13 bit12 bit11 bit10 bit9 bit8

XXXXXXXXB

R : Read only

X : Undefined

Reset value

Address

IPCP0 (upper): 007921

H

IPCP0 (lower): 007920H

IPCP1 (upper): 007923H

IPCP1 (lower): 007922

H

IPCP2 (upper): 007925

H

IPCP2 (lower): 007924

H

IPCP3 (upper): 007927

H

IPCP3 (lower): 007926

H