214

CHAPTER 13 16-Bit I/O TIMER

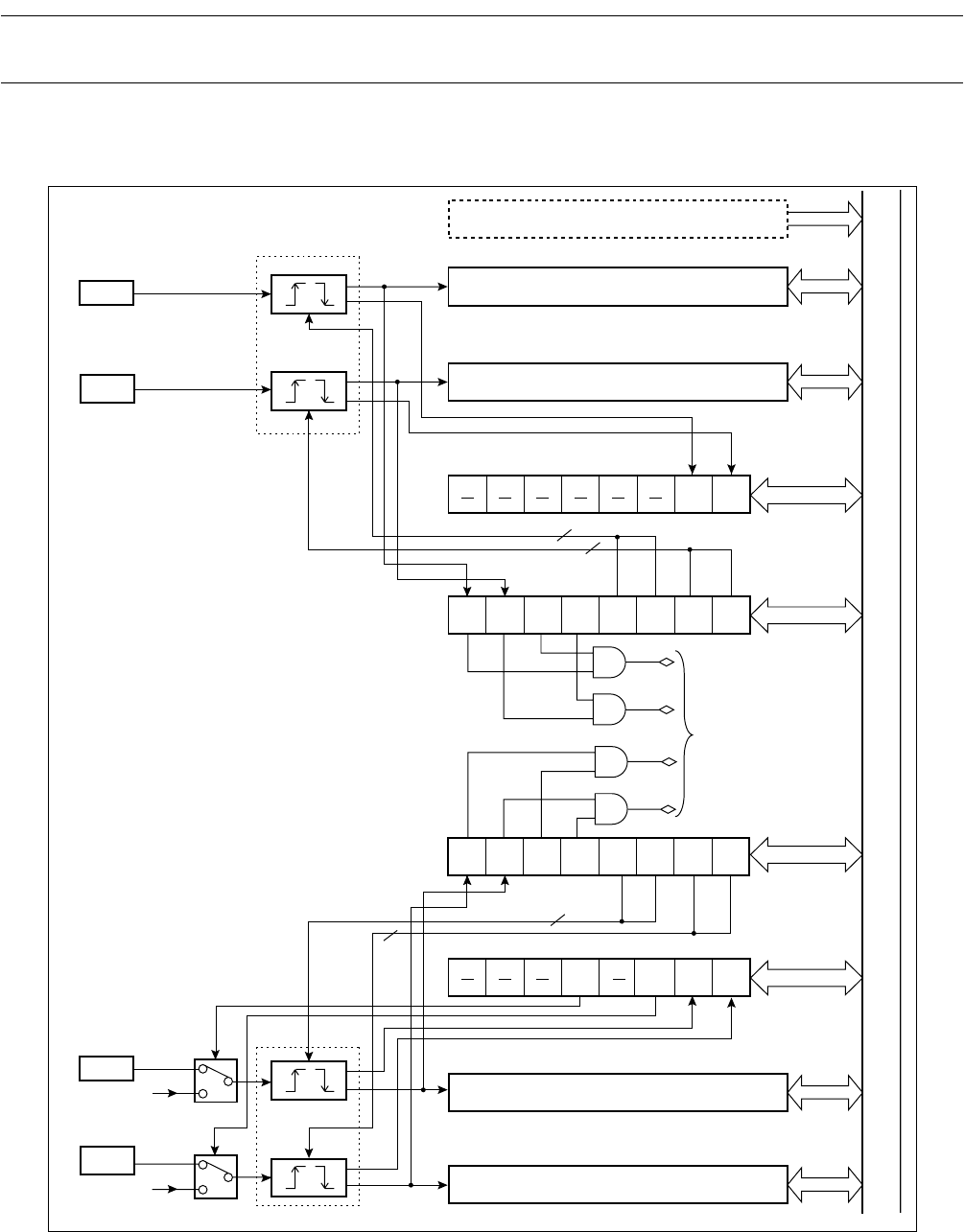

13.2.2 Block Diagram of Input Capture

The input capture consist of the following blocks:

■ Block Diagram of Input Capture

Figure 13.2-3 Block Diagram of Input Capture Unit 0

EG20EG21EG30EG31ICE2

2

2

EG00EG01EG10EG11ICE0ICE1ICP0ICP1

ICE3ICP2

ICP3

IEI2IEI3

ICUS0

ICUS1

IEI0IEI1

2

2

IN1

LIN-UART1

LIN-UART0

IN0

IN3

IN2

Input capture data register 0 (IPCP0)

Pin

Pin

Pin

Pin

Input capture data register 1 (IPCP1)

Input capture control

status register (ICS01)

Input capture control

status register (ICS23)

Input capture

interrupt request

Internal data bus

Input capture edge

register (ICE23)

16-bit free-run timer

Input capture data register 3 (IPCP3)

Input capture data register 2 (IPCP2)

Edge detection circuit

Input capture edge register (ICE01)

Edge detection circuit